# Network Systems Design (CS490N)

**Douglas Comer**

Computer Science Department Purdue University West Lafayette, IN 47907

http://www.cs.purdue.edu/people/comer

© Copyright 2003. All rights reserved. This document may not be reproduced by any means without the express written consent of the author.

#### I

# **Course Introduction And Overview**

### **Topic And Scope**

The concepts, principles, and technologies that underlie the design of hardware and software systems used in computer networks and the Internet, focusing on the emerging field of network processors.

#### You Will Learn

- Review of

- Network systems

- Protocols and protocol processing tasks

- Hardware architectures for protocol processing

- Software-based network systems and software architectures

- Classification

- Concept

- Software implementation

- Special languages

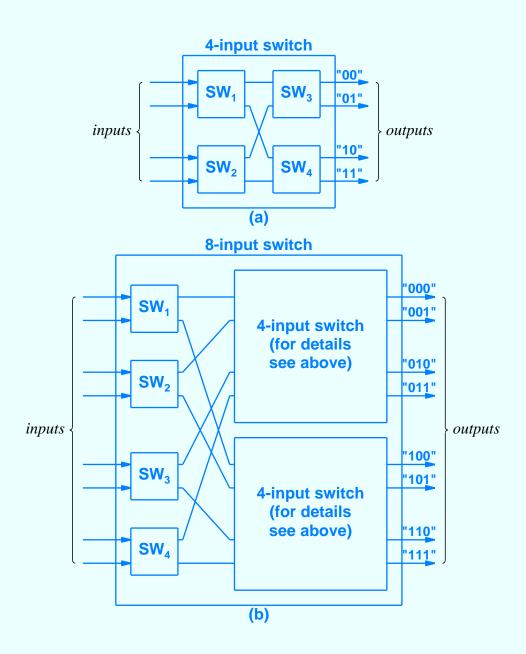

- Switching fabrics

# You Will Learn (continued)

- Network processors: definition, architectures, and use

- Design tradeoffs and consequences

- Survey of commercial network processors

- Details of one example network processor

- Architecture and instruction set(s)

- Programming model and program optimization

- Cross-development environment

#### What You Will NOT Learn

- EE details

- VLSI technology and design rules

- Chip interfaces: ICs and pin-outs

- Waveforms, timing, or voltage

- How to wire wrap or solder

- Economic details

- Comprehensive list of vendors and commercial products

- Price points

# **Background Required**

- Basic knowledge of

- Network and Internet protocols

- Packet headers

- Basic understanding of hardware architecture

- Registers

- Memory organization

- Typical instruction set

- Willingness to use an assembly language

## **Schedule Of Topics**

- Quick review of basic networking

- Protocol processing tasks and classification

- Software-based systems using conventional hardware

- Special-purpose hardware for high speed

- Motivation and role of network processors

- Network processor architectures

# **Schedule Of Topics** (continued)

- An example network processor technology in detail

- Hardware architecture and parallelism

- Programming model

- Testbed architecture and features

- Design tradeoffs

- Scaling a network processor

- Classification languages and programs

#### **Course Administration**

#### Textbook

– D. Comer, *Network Systems Design Using Network Processors*, Prentice Hall, 2003.

#### Grade

- Quizzes 5%

- Midterm and final exam 35%

- Programming projects 60%

### Lab Facilities Available

- Extensive network processor testbed facilities (more than any other university)

- Donations from

- Agere Systems

- IBM

- Intel

- Includes hardware and cross-development software

#### What You Will Do In The Lab

- Write and compile software for an NP

- Download software into an NP

- Monitor the NP as it runs

- Interconnect Ethernet ports on an NP board

- To other ports on other NP boards

- To other computers in the lab

- Send Ethernet traffic to the NP

- Receive Ethernet traffic from the NP

# **Programming Projects**

- A packet analyzer

- IP datagrams

- TCP segments

- An Ethernet bridge

- An IP fragmenter

- A classification program

- A bump-in-the-wire system using low-level packet processors

# A QUICK OVERVIEW OF NETWORK PROCESSORS

# The Network Systems Problem

- Data rates keep increasing

- Protocols and applications keep evolving

- System design is expensive

- System implementation and testing take too long

- Systems often contain errors

- Special-purpose hardware designed for one system cannot be reused

### The Challenge

Find ways to improve the design and manufacture of complex networking systems.

## The Big Questions

- What systems?

- Everything we have now

- New devices not yet designed

- What physical communication mechanisms?

- Everything we have now

- New communication systems not yet designed / standardized

- What speeds?

- Everything we have now

- New speeds much faster than those in use

# **More Big Questions**

- What protocols?

- Everything we have now

- New protocols not yet designed / standardized

- What applications?

- Everything we have now

- New applications not yet designed/standardized

# The Challenge (restated)

Find flexible, general technologies that enable rapid, low-cost design and manufacture of a variety of scalable, robust, efficient network systems that run a variety of existing and new protocols, perform a variety of existing and new functions for a variety of existing and new, higher-speed networks to support a variety of existing and new applications.

# **Special Difficulties**

- Ambitious goal

- Vague problem statement

- Problem is evolving with the solution

- Pressure from

- Changing infrastructure

- Changing applications

### **Desiderata**

- High speed

- Flexible and extensible to accommodate

- Arbitrary protocols

- Arbitrary applications

- Arbitrary physical layer

- Low cost

### **Desiderata**

- High speed

- Flexible and extensible to accommodate

- Arbitrary protocols

- Arbitrary applications

- Arbitrary physical layer

- Low cost

# Statement Of Hope (1995 version)

If there is hope, it lies in ASIC designers.

# **Statement Of Hope** (1999 version)

???

If there is hope, it lies in ASIC designers.

# Statement Of Hope (2003 version)

programmers!

If there is hope, it lies in ASIC designers.

## **Programmability**

- Key to low-cost hardware for next generation network systems

- More flexibility than ASIC designs

- Easier / faster to update than ASIC designs

- Less expensive to develop than ASIC designs

- What we need: a programmable device with more capability than a conventional CPU

#### The Idea In A Nutshell

- Devise new hardware building blocks

- Make them programmable

- Include support for protocol processing and I/O

- General-purpose processor(s) for control tasks

- Special-purpose processor(s) for packet processing and table lookup

- Include functional units for tasks such as checksum computation

- Integrate as much as possible onto one chip

- Call the result a *network processor*

#### The Rest Of The Course

- We will

- Examine general problem being solved

- Survey some approaches vendors have taken

- Explore possible architectures

- Study example technologies

- Consider how to implement systems using network processors

### **Disclaimer #1**

In the field of network processors, I am a tyro.

#### **Definition**

Tyro  $\langle Ty'ro \rangle$ , n.; pl. *Tyros*. A beginner in learning; one who is in the rudiments of any branch of study; a person imperfectly acquainted with a subject; a novice.

# **By Definition**

In the field of network processors, you are all tyros.

### In Our Defense

When it comes to network processors, everyone is a tyro.

#### II

# Basic Terminology And Example Systems (A Quick Review)

#### **Packets Cells And Frames**

- Packet

- Generic term

- Small unit of data being transferred

- Travels independently

- Upper and lower bounds on size

# Packets Cells And Frames (continued)

- Cell

- Fixed-size packet (e.g., ATM)

- Frame or layer-2 packet

- Packet understood by hardware

- IP datagram

- Internet packet

## **Types Of Networks**

- Paradigm

- Connectionless

- Connection-oriented

- Access type

- Shared (i.e., multiaccess)

- Point-To-Point

#### **Point-To-Point Network**

- Connects exactly two systems

- Often used for long distance

- Example: data circuit connecting two routers

#### **Data Circuit**

- Leased from phone company

- Also called *serial line* because data is transmitted bitserially

- Originally designed to carry digital voice

- Cost depends on speed and distance

- T-series standards define low speeds (e.g. T1)

- STS and OC standards define high speeds

## **Digital Circuit Speeds**

| Standard Name | Bit Rate        | <b>Voice Circuits</b> |  |

|---------------|-----------------|-----------------------|--|

| _             | 0.064 Mbps      | 1                     |  |

| T1            | 1.544 Mbps      | 24                    |  |

| T3            | 44.736 Mbps     | 672                   |  |

| OC-1          | 51.840 Mbps     | 810                   |  |

| OC-3          | 155.520 Mbps    | 2430                  |  |

| OC-12         | 622.080 Mbps    | 9720                  |  |

| OC-24         | 1,244.160 Mbps  | 19440                 |  |

| OC-48         | 2,488.320 Mbps  | 38880                 |  |

| OC-192        | 9,953.280 Mbps  | 155520                |  |

| OC-768        | 39,813.120 Mbps | 622080                |  |

#### **Digital Circuit Speeds**

| Standard Name | Bit Rate        | <b>Voice Circuits</b> |  |

|---------------|-----------------|-----------------------|--|

| _             | 0.064 Mbps      | 1                     |  |

| T1            | 1.544 Mbps      | 24                    |  |

| <b>T3</b>     | 44.736 Mbps     | <b>672</b>            |  |

| OC-1          | 51.840 Mbps     | 810                   |  |

| OC-3          | 155.520 Mbps    | 2430                  |  |

| OC-12         | 622.080 Mbps    | 9720                  |  |

| OC-24         | 1,244.160 Mbps  | 19440                 |  |

| OC-48         | 2,488.320 Mbps  | 38880                 |  |

| OC-192        | 9,953.280 Mbps  | 155520                |  |

| OC-768        | 39,813.120 Mbps | 622080                |  |

• Holy grail of networking: devices capable of accepting and forwarding data at 10 Gbps (OC-192).

#### **Local Area Networks**

- Ethernet technology dominates

- Layer 1 standards

- Media and wiring

- Signaling

- Handled by dedicated interface chips

- Unimportant to us

- Layer 2 standards

- MAC framing and addressing

### **MAC Addressing**

- Three address types

- Unicast (single computer)

- Broadcast (all computers in broadcast domain)

- Multicast (some computers in broadcast domain)

### **More Terminology**

- Internet

- Interconnection of multiple networks

- Allows heterogeneity of underlying networks

- Network scope

- Local Area Network (LAN) covers limited distance

- Wide Area Network (WAN) covers arbitrary distance

### **Network System**

- Individual hardware component

- Serves as fundamental building block

- Used in networks and internets

- May contain processor and software

- Operates at one or more layers of the protocol stack

## **Example Network Systems**

- Layer 2

- Bridge

- Ethernet switch

- VLAN switch

#### **VLAN Switch**

- Similar to conventional layer 2 switch

- Connects multiple computers

- Forwards frames among them

- Each computer has unique unicast address

- Differs from conventional layer 2 switch

- Allows manager to configure broadcast domains

- Broadcast domain known as *virtual* network

#### **Broadcast Domain**

- Determines propagation of broadcast/multicast

- Originally corresponded to fixed hardware

- One per cable segment

- One per hub or switch

- Now configurable via VLAN switch

- Manager assigns ports to VLANs

# **Example Network Systems** (continued)

- Layer 3

- Internet host computer

- IP router (layer 3 switch)

- Layer 4

- Basic Network Address Translator (NAT)

- Round-robin Web load balancer

- TCP terminator

# **Example Network Systems** (continued)

- Layer 5

- Firewall

- Intrusion Detection System (IDS)

- Virtual Private Network (VPN)

- Softswitch running SIP

- Application gateway

- TCP splicer (also known as NAPT Network Address and Protocol Translator)

- Smart Web load balancer

- Set-top box

# **Example Network Systems** (continued)

- Network control systems

- Packet/flow analyzer

- Traffic monitor

- Traffic policer

- Traffic shaper

#### III

#### **Review Of Protocols And Packet Formats**

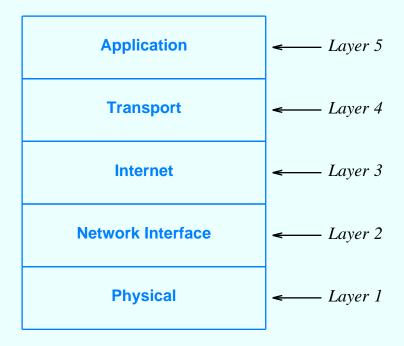

### **Protocol Layering**

- Five-layer Internet reference model

- Multiple protocols can occur at each layer

### **Layer 2 Protocols**

- Two protocols are important

- Ethernet

- ATM

- We will concentrate on Ethernet

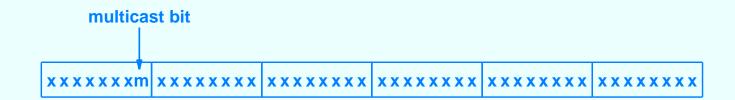

### **Ethernet Addressing**

- 48-bit addressing

- Unique address assigned to each station (NIC)

- Destination address in each packet can specify delivery to

- A single computer (unicast)

- All computers in broadcast domain (broadcast)

- Some computers in broadcast domain (multicast)

## **Ethernet Addressing** (continued)

- Broadcast address is all 1s

- Single bit determines whether remaining addresses are unicast or multicast

#### **Ethernet Frame Processing**

| Dest.<br>Address | Source F<br>Address |   |           |

|------------------|---------------------|---|-----------|

| 6                | 6                   | 2 | 46 - 1500 |

| <b>←</b> H       | leader ——           |   | Payload — |

- Dedicated physical layer hardware

- Checks and removes preamble and CRC on input

- Computes and appends CRC and preamble on output

- Layer 2 systems use source, destination and (possibly) type fields

#### **Internet**

- Set of (heterogeneous) computer networks interconnected by *IP routers*

- End-user computers, called *hosts*, each attach to specific network

- Protocol software

- Runs on both hosts and routers

- Provides illusion of homogeneity

#### **Internet Protocols Of Interest**

- Layer 2

- Address Resolution Protocol (ARP)

- Layer 3

- Internet Protocol (IP)

- Layer 4

- User Datagram Protocol (UDP)

- Transmission Control Protocol (TCP)

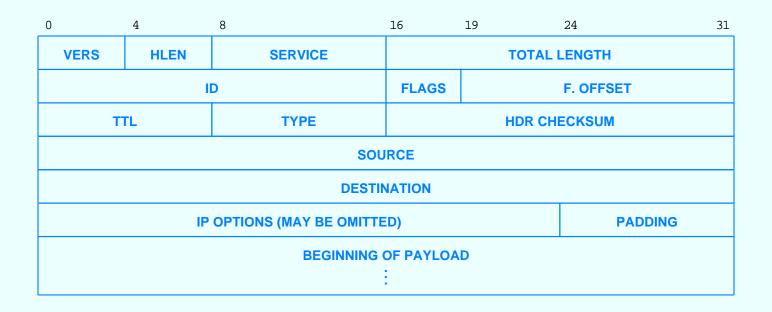

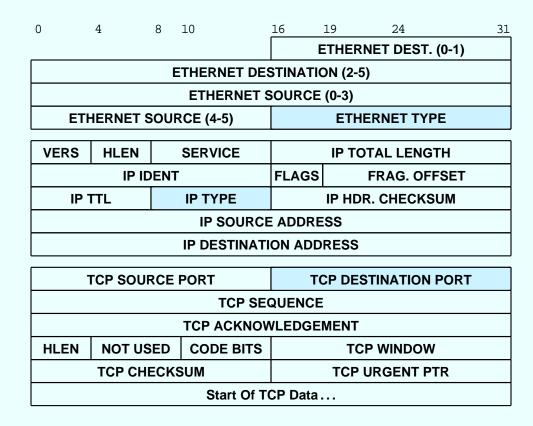

#### **IP Datagram Format**

- Format of each packet sent across Internet

- Fixed-size fields make parsing efficient

## **IP Datagram Fields**

| Field               | Meaning                                    |  |  |

|---------------------|--------------------------------------------|--|--|

| VERS                | Version number of IP being used (4)        |  |  |

| HLEN                | Header length measured in 32-bit units     |  |  |

| SERVICE             | Level of service desired                   |  |  |

| <b>TOTAL LENGTH</b> | Datagram length in octets including header |  |  |

| ID                  | Unique value for this datagram             |  |  |

| FLAGS               | Bits to control fragmentation              |  |  |

| F. OFFSET           | Position of fragment in original datagram  |  |  |

| TTL                 | Time to live (hop countdown)               |  |  |

| TYPE                | Contents of payload area                   |  |  |

| HDR CHECKSUM        | One's-complement checksum over header      |  |  |

| SOURCE              | IP address of original sender              |  |  |

| <b>DESTINATION</b>  | IP address of ultimate destination         |  |  |

| <b>IP OPTIONS</b>   | Special handling parameters                |  |  |

| PADDING             | To make options a 32-bit multiple          |  |  |

### IP addressing

- 32-bit Internet address assigned to each computer

- Virtual, hardware independent value

- Prefix identifies network; suffix identifies host

- Network systems use address mask to specify boundary between prefix and suffix

## **Next-Hop Forwarding**

- Routing table

- Found in both hosts and routers

- Stores (destination, mask, next\_hop) tuples

- Route lookup

- Takes destination address as argument

- Finds next hop

- Uses longest-prefix match

### **Next-Hop Forwarding**

- Routing table

- Found in both hosts and routers

- Stores (destination, mask, next\_hop) tuples

- Route lookup

- Takes destination address as argument

- Finds next hop

- Uses longest-prefix match

## **UDP Datagram Format**

| 0                    | 16 31            |  |  |  |

|----------------------|------------------|--|--|--|

| SOURCE PORT          | DESTINATION PORT |  |  |  |

| MESSAGE LENGTH       | CHECKSUM         |  |  |  |

| BEGINNING OF PAYLOAD |                  |  |  |  |

|                      |                  |  |  |  |

|                      |                  |  |  |  |

| Field                   | Meaning                                        |

|-------------------------|------------------------------------------------|

| SOURCE PORT             | ID of sending application                      |

| <b>DESTINATION PORT</b> | ID of receiving application                    |

| MESSAGE LENGTH          | Length of datagram including the header        |

| CHECKSUM                | One's-complement checksum over entire datagram |

## **TCP Segment Format**

| 0                        | 4 10            |  | 16       | 24 31     |  |

|--------------------------|-----------------|--|----------|-----------|--|

| SOURCE PORT              |                 |  | DESTINAT | TION PORT |  |

| SEQUENCE                 |                 |  |          |           |  |

|                          | ACKNOWLEDGEMENT |  |          |           |  |

| HLEN NOT USED CODE BITS  |                 |  | WINDOW   |           |  |

| CHECKSUM                 |                 |  | URGEI    | NT PTR    |  |

| OPTIONS (MAY BE OMITTED) |                 |  |          | PADDING   |  |

| BEGINNING OF PAYLOAD     |                 |  |          |           |  |

|                          |                 |  |          |           |  |

- Sent end-to-end

- Fixed-size fields make parsing efficient

## **TCP Segment Fields**

| Field                   | Meaning                                       |

|-------------------------|-----------------------------------------------|

| SOURCE PORT             | ID of sending application                     |

| <b>DESTINATION PORT</b> | ID of receiving application                   |

| SEQUENCE                | Sequence number for data in payload           |

| <b>ACKNOWLEDGEMENT</b>  | Acknowledgement of data received              |

| HLEN                    | Header length measured in 32-bit units        |

| NOT USED                | Currently unassigned                          |

| CODE BITS               | URGENT, ACK, PUSH, RESET, SYN, FIN            |

| WINDOW                  | Receiver's buffer size for additional data    |

| CHECKSUM                | One's-complement checksum over entire segment |

| URGENT PTR              | Pointer to urgent data in segment             |

| OPTIONS                 | Special handling                              |

| PADDING                 | To make options a 32-bit multiple             |

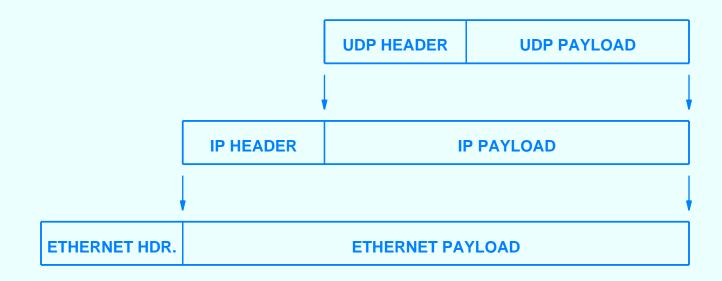

#### **Illustration Of Encapsulation**

• Field in each header specifies type of encapsulated packet

#### **Example ARP Packet Format**

| 0                                  | 8                   | 16 | 24                               | 31 |  |

|------------------------------------|---------------------|----|----------------------------------|----|--|

| ETHERNET ADDRESS TYPE (1)          |                     |    | IP ADDRESS TYPE (0800)           |    |  |

| ETH ADDR LEN (6) IP ADDR LEN (4)   |                     |    | OPERATION                        |    |  |

| SENDER'S ETH ADDR (first 4 octets) |                     |    |                                  |    |  |

| SENDER'S ETH ADDR (last 2 octets)  |                     | S  | ENDER'S IP ADDR (first 2 octets) |    |  |

| SENDER'S IP AD                     | DDR (last 2 octets) | TA | RGET'S ETH ADDR (first 2 octets) |    |  |

| TARGET'S ETH ADDR (last 4 octets)  |                     |    |                                  |    |  |

| TARGET'S IP ADDR (all 4 octets)    |                     |    |                                  |    |  |

- Format when ARP used with Ethernet and IP

- Each Ethernet address is six octets

- Each IP address is four octets

#### IV

# **Conventional Computer Hardware Architecture**

#### **Software-Based Network System**

- Uses conventional hardware (e.g., PC)

- Software

- Runs the entire system

- Allocates memory

- Controls I/O devices

- Performs all protocol processing

# Why Study Protocol Processing On Conventional Hardware?

#### Past

- Employed in early IP routers

- Many algorithms developed/optimized for conventional hardware

#### Present

- Used in low-speed network systems

- Easiest to create/modify

- Costs less than special-purpose hardware

# Why Study Protocol Processing On Conventional Hardware? (continued)

- Future

- Processors continue to increase in speed

- Some conventional hardware present in all systems

# Why Study Protocol Processing On Conventional Hardware? (continued)

#### Future

- Processors continue to increase in speed

- Some conventional hardware present in all systems

- You will build software-based systems in lab!

#### **Serious Question**

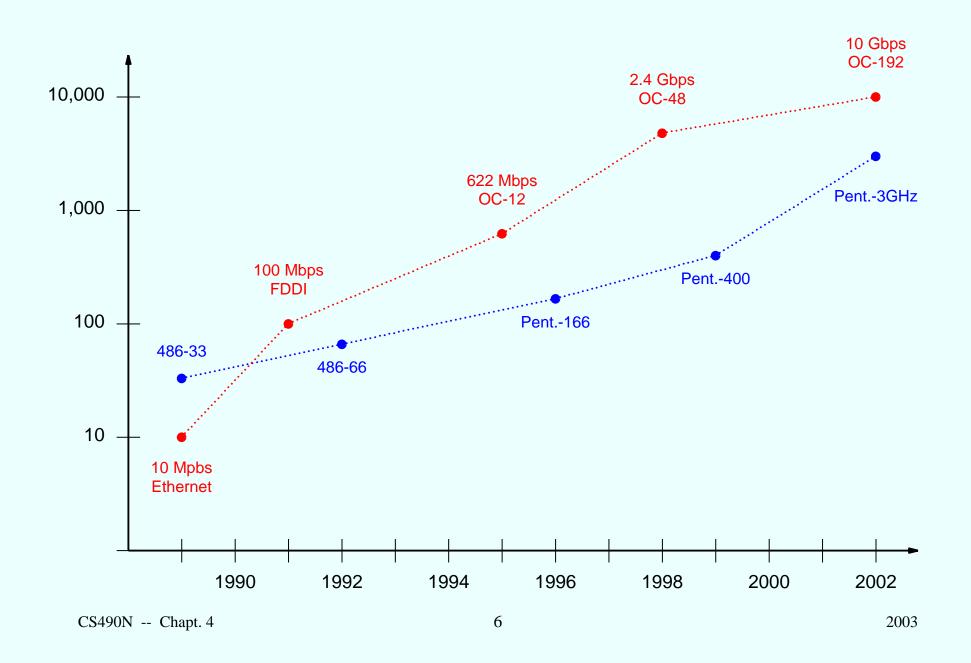

- Which is growing faster?

- Processing power

- Network bandwidth

- Note: if network bandwidth growing faster

- Need special-purpose hardware

- Conventional hardware will become irrelevant

# **Growth Of Technologies**

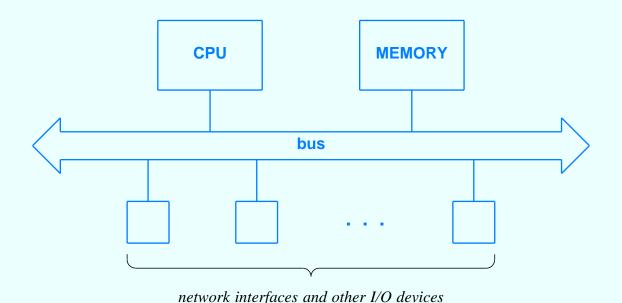

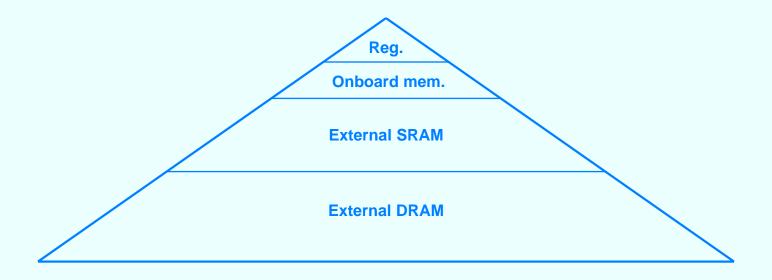

# **Conventional Computer Hardware**

- Four important aspects

- Processor

- Memory

- I/O interfaces

- One or more buses

# Illustration Of Conventional Computer Architecture

• Bus is central, shared interconnect

• All components *contend* for use

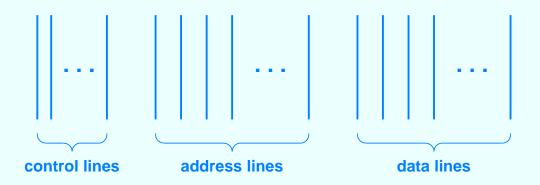

#### **Bus Organization And Operations**

- Parallel wires (K+N+C total)

- Used to pass

- An address of K bits

- A data value of N bits (width of the bus)

- Control information of C bits

#### **Bus Width**

- Wider bus

- Transfers more data per unit time

- Costs more

- Requires more physical space

- Compromise: to simulate wider bus, use hardware that multiplexes transfers

#### **Bus Paradigm**

- Only two basic operations

- Fetch

- Store

- All operations cast as forms of the above

#### Fetch/Store

- Fundamental paradigm

- Used throughout hardware, including network processors

#### **Fetch Operation**

- Place address of a device on address lines

- Issue *fetch* on control lines

- Wait for device that owns the address to respond

- If successful, extract value (response) from data lines

#### **Store Operation**

- Place address of a device on address lines

- Place value on data lines

- Issue *store* on control lines

- Wait for device that owns the address to respond

- If unsuccessful, report error

# **Example Of Operations Mapped Into Fetch/Store Paradigm**

- Imagine disk device attached to a bus

- Assume the hardware can perform three (nontransfer) operations:

- Start disk spinning

- Stop disk

- Determine current status

# Example Of Operations Mapped Into Fetch/Store Paradigm (continued)

- Assign the disk two contiguous bus addresses D and D+1

- Arrange for store of nonzero to address D to start disk spinning

- Arrange for store of zero to address D to stop disk

- Arrange for fetch from address D+1 to return current status

- Note: effect of store to address D+1 can be defined as

- Appears to work, but has no effect

- Returns an error

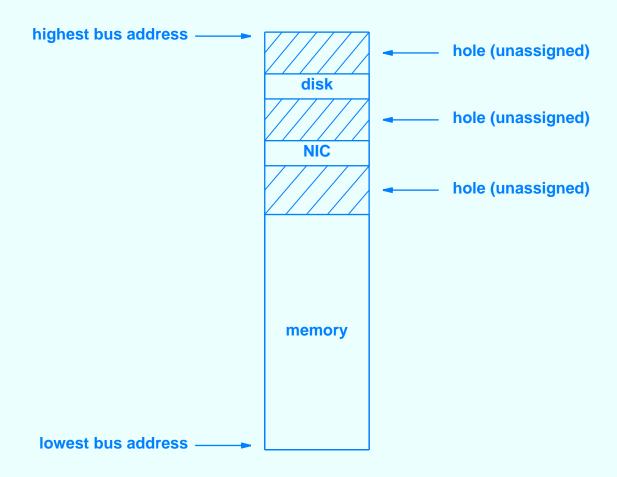

#### **Bus Address Space**

- Arbitrary hardware can be attached to bus

- K address lines result in 2<sup>k</sup> possible bus addresses

- Address can refer to

- Memory (e.g., RAM or ROM)

- I/O device

- Arbitrary devices can be placed at arbitrary addresses

- Address space can contain "holes"

#### **Bus Address Terminology**

- Device on bus known as *memory mapped* I/O

- Locations that correspond to nontransfer operations known as *Control and Status Registers (CSRs)*

# **Example Bus Address Space**

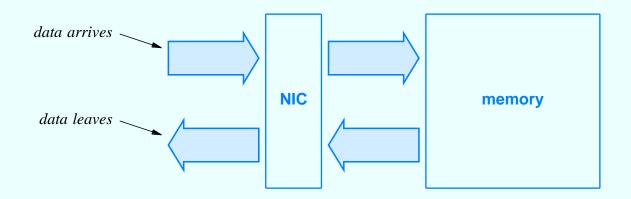

## Network I/O On Conventional Hardware

- Network Interface Card (NIC)

- Attaches between bus and network

- Operates like other I/O devices

- Handles electrical/optical details of network

- Handles electrical details of bus

- Communicates over bus with CPU or other devices

#### **Making Network I/O Fast**

- Key idea: migrate more functionality onto NIC

- Four techniques used with bus

- Onboard address recognition & filtering

- Onboard packet buffering

- Direct Memory Access (DMA)

- Operation and buffer chaining

# **Onboard Address Recognition And Filtering**

- NIC given set of addresses to accept

- Station's unicast address

- Network broadcast address

- Zero or more multicast addresses

- When packet arrives, NIC checks destination address

- Accept packet if address on list

- Discard others

# **Onboard Packet Buffering**

- NIC given high-speed local memory

- Incoming packet placed in NIC's memory

- Allows computer's memory/bus to operate slower than network

- Handles small packet bursts

#### **Direct Memory Access (DMA)**

#### • CPU

- Allocates packet buffer in memory

- Passes buffer address to NIC

- Goes on with other computation

#### NIC

- Accepts incoming packet from network

- Copies packet over bus to buffer in memory

- Informs CPU that packet has arrived

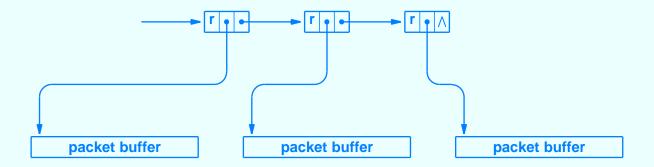

#### **Buffer Chaining**

- CPU

- Allocates multiple buffers

- Passes linked list to NIC

- NIC

- Receives next packet

- Divides into one or more buffers

- Advantage: a buffer can be smaller than packet

# **Operation Chaining**

#### • CPU

- Allocates multiple buffers

- Builds linked list of operations

- Passes list to NIC

- NIC

- Follows list and performs instructions

- Interrupts CPU after each operation

- Advantage: multiple operations proceed without CPU intervention

# **Illustration Of Operation Chaining**

Optimizes movement of data to memory

#### **Data Flow Diagram**

- Depicts flow of data through hardware units

- Used throughout the course and text

#### **Summary**

- Software-based network systems run on conventional hardware

- Processor

- Memory

- I/O devices

- Bus

- Network interface cards can be optimized to reduce CPU load

#### V

# **Basic Packet Processing: Algorithms And Data Structures**

# **Copying**

- Used when packet moved from one memory location to another

- Expensive

- Must be avoided whenever possible

- Leave packet in buffer

- Pass buffer address among threads/layers

#### **Buffer Allocation**

- Possibilities

- Large, fixed buffers

- Variable-size buffers

- Linked list of fixed-size blocks

#### **Buffer Addressing**

- Buffer address must be resolvable in all contexts

- Easiest implementation: keep buffers in kernel space

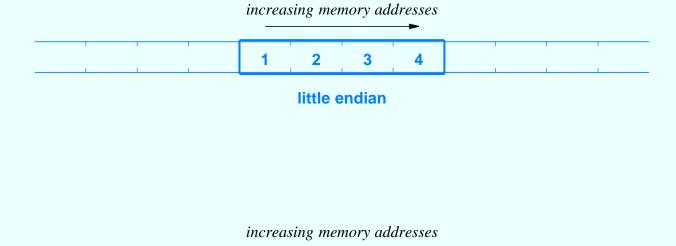

#### **Integer Representation**

- Two standards

- Little endian (least-significant byte at lowest address)

- Big endian (most-significant byte at lowest address)

## Illustration Of Big And Little Endian Integers

big endian

### **Integer Conversion**

- Needed when heterogeneous computers communicate

- Protocols define network byte order

- Computers convert to network byte order

- Typical library functions

| <b>Function</b> | data size | Translation                             |

|-----------------|-----------|-----------------------------------------|

| ntohs           | 16 bits   | Network byte order to host's byte order |

| htons           | 16 bits   | Host's byte order to network byte order |

| ntohl           | 32 bits   | Network byte order to host's byte order |

| htonl           | 32 bits   | Host's byte order to network byte order |

# **Examples Of Algorithms Implemented With Software-Based Systems**

- Layer 2

- Ethernet bridge

- Layer 3

- IP forwarding

- IP fragmentation and reassembly

- Layer 4

- TCP connection recognition and splicing

- Other

- Hash table lookup

Provide insight on packet processing tasks

- Provide insight on packet processing tasks

- Reinforce concepts

- Provide insight on packet processing tasks

- Reinforce concepts

- Help students recall protocol details

- Provide insight on packet processing tasks

- Reinforce concepts

- Help students recall protocol details

- You will need them in lab!

### **Ethernet Bridge**

- Used between a pair of Ethernets

- Provides transparent connection

- Listens in promiscuous mode

- Forwards frames in both directions

- Uses addresses to filter

## **Bridge Filtering**

- Uses source address in frames to identify computers on each network

- Uses destination address to decide whether to forward frame

#### **Bridge Algorithm**

```

Assume: two network interfaces each operating in promiscuous

mode.

Create an empty list, L, that will contain pairs of values;

Do forever {

Acquire the next frame to arrive;

Set I to the interface over which the frame arrived;

Extract the source address, S;

Extract the destination address, D;

Add the pair (S, I) to list L if not already present.

If the pair (D, I) appears in list L {

Drop the frame;

} Else {

Forward the frame over the other interface;

```

## **Implementation Of Table Lookup**

- Need high speed (more on this later)

- Software-based systems typically use hashing for table lookup

## **Hashing**

- Optimizes number of *probes*

- Works well if table not full

- Practical technique: double hashing

#### **Hashing Algorithm**

```

Given: a key, a table in memory, and the table size N.

Produce: a slot in the table that corresponds to the key

or an empty table slot if the key is not in the table.

Method: double hashing with open addressing.

Choose P_1 and P_2 to be prime numbers;

Fold the key to produce an integer, K;

Compute table pointer Q equal to (P_1 \times K) modulo N;

Compute increment R equal to (P_2 \times K) modulo N;

While (table slot Q not equal to K and nonempty) {

Q \leftarrow (Q + R) \text{ modulo } N;

At this point, Q either points to an empty table slot or to the

slot containing the key.

```

#### **Address Lookup**

- Computer can compare integer in one operation

- Network address can be longer than integer (e.g., 48 bits)

- Two possibilities

- Use multiple comparisons per probe

- Fold address into integer key

## **Folding**

- Maps N-bit value into M-bit key, M < N

- Typical technique: exclusive or

- Potential problem: two values map to same key

- Solution: compare full value when key matches

### **IP Forwarding**

- Used in hosts as well as routers

- Conceptual mapping

```

(next hop, interface) \leftarrow f(\text{datagram, routing table})

```

• Table driven

## **IP Routing Table**

- One entry per destination

- Entry contains

- 32-bit IP address of destination

- 32-bit address mask

- 32-bit next-hop address

- N-bit interface number

#### **Example IP Routing Table**

| Destination    | <b>Address</b> | <b>Next-Hop</b> | Interface |

|----------------|----------------|-----------------|-----------|

| <b>Address</b> | Mask           | Address         | Number    |

| 192.5.48.0     | 255.255.255.0  | 128.210.30.5    | 2         |

| 128.10.0.0     | 255.255.0.0    | 128.210.141.12  | 1         |

| 0.0.0.0        | 0.0.0.0        | 128.210.30.5    | 2         |

- Values stored in binary

- Interface number is for internal use only

- Zero mask produces *default* route

#### **IP Forwarding Algorithm**

```

Given: destination address A and routing table R.

Find: a next hop and interface used to route datagrams to A.

For each entry in table R {

Set MASK to the Address Mask in the entry;

Set DEST to the Destination Address in the entry;

If (A & MASK) == DEST {

Stop; use the next hop and interface in the entry;

}

If this point is reached, declare error: no route exists;

```

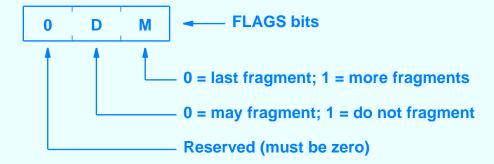

#### **IP Fragmentation**

- Needed when datagram larger than network MTU

- Divides IP datagram into *fragments*

- Uses FLAGS bits in datagram header

# IP Fragmentation Algorithm (Part 1: Initialization)

```

Given: an IP datagram, D, and a network MTU.

Produce: a set of fragments for D.

If the DO NOT FRAGMENT bit is set {

Stop and report an error;

}

Compute the size of the datagram header, H;

Choose N to be the largest multiple of 8 such that H+N≤MTU;

Initialize an offset counter, O, to zero;

```

# IP Fragmentation Algorithm (Part 2: Processing)

```

Repeat until datagram empty {

Create a new fragment that has a copy of D's header;

Extract up to the next N octets of data from D and place

the data in the fragment;

Set the MORE FRAGMENTS bit in fragment header;

Set TOTAL LENGTH field in fragment header to be H+N;

Set FRAGMENT OFFSET field in fragment header to O;

Compute and set the CHECKSUM field in fragment

header;

Increment O by N/8;

```

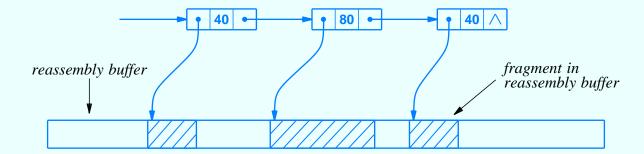

## Reassembly

- Complement of fragmentation

- Uses IP SOURCE ADDRESS and IDENTIFICATION fields in datagram header to group related fragments

- Joins fragments to form original datagram

#### **Reassembly Algorithm**

```

Given: a fragment, F, add to a partial reassembly.

Method: maintain a set of fragments for each datagram.

Extract the IP source address, S, and ID fields from F;

Combine S and ID to produce a lookup key, K;

Find the fragment set with key K or create a new set;

Insert F into the set;

If the set contains all the data for the datagram {

Form a completely reassembled datagram and process it;

}

```

### **Data Structure For Reassembly**

- Two parts

- Buffer large enough to hold original datagram

- Linked list of pieces that have arrived

#### **TCP Connection**

- Involves a pair of endpoints

- Started with SYN segment

- Terminated with FIN or RESET segment

- Identified by 4-tuple

(src addr, dest addr, src port, dest port)

# TCP Connection Recognition Algorithm (Part 1)

Given: a copy of traffic passing across a network.

Produce: a record of TCP connections present in the traffic.

Initialize a connection table, C, to empty;

For each IP datagram that carries a TCP segment {

Extract the IP source, S, and destination, D, addresses;

Extract the source,  $P_1$ , and destination,  $P_2$ , port numbers;

Use (S,D,P<sub>1</sub>,P<sub>2</sub>) as a lookup key for table C and create a new entry, if needed;

# TCP Connection Recognition Algorithm (Part 2)

If the segment has the RESET bit set, delete the entry;

Else if the segment has the FIN bit set, mark the connection

closed in one direction, removing the entry from C if the connection was previously closed in the other;

Else if the segment has the SYN bit set, mark the connection as

being established in one direction, making it completely established if it was previously marked as being established in the other;

}

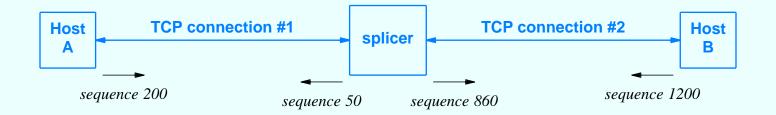

### **TCP Splicing**

- Join two TCP connections

- Allow data to pass between them

- To avoid termination overhead translate segment header fields

- Acknowledgement number

- Sequence number

## **Illustration Of TCP Splicing**

| Connection  | Sequence | Connection  | Sequence  |

|-------------|----------|-------------|-----------|

| & Direction | Number   | & Direction | Number    |

| Incoming #1 | 200      | Incoming #2 | 1200      |

| Outgoing #2 | 860      | Outgoing #1 | <b>50</b> |

| Change      | 660      | Change      | -1150     |

# TCP Splicing Algorithm (Part 1)

Given: two TCP connections.

Produce: sequence translations for splicing the connection.

Compute D1, the difference between the starting sequences on incoming connection 1 and outgoing connection 2;

Compute D2, the difference between the starting sequences on incoming connection 2 and outgoing connection 1;

## TCP Splicing Algorithm (Part 2)

```

For each segment {

If segment arrived on connection 1 {

Add D1 to sequence number;

Subtract D2 from acknowledgement number;

} else if segment arrived on connection 2 {

Add D2 to sequence number;

Subtract D1 from acknowledgement number;

```

### **Summary**

- Packet processing algorithms include

- Ethernet bridging

- IP fragmentation and reassembly

- IP forwarding

- TCP splicing

- Table lookup important

- Full match for layer 2

- Longest prefix match for layer 3

## For Hands-On Experience With

A Software-Based System:

Enroll in CS 636!

#### VI

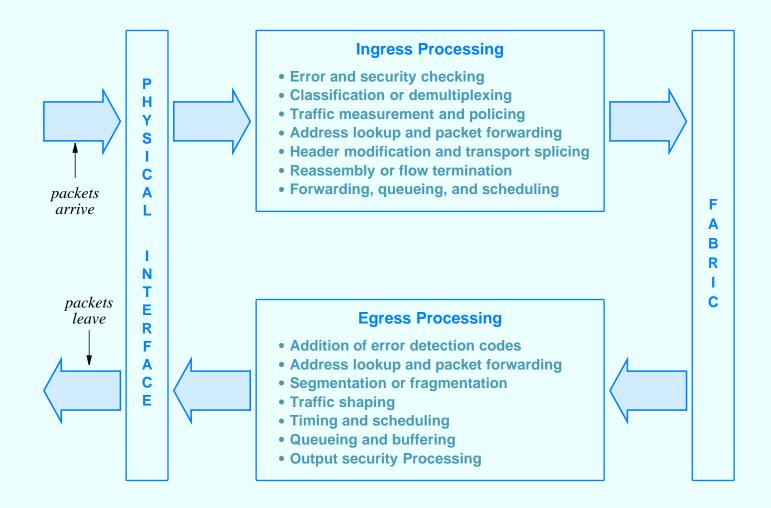

## **Packet Processing Functions**

#### Goal

- Identify functions that occur in packet processing

- Devise set of operations sufficient for all packet processing

- Find an efficient implementation for the operations

### **Packet Processing Functions We Will Consider**

- Address lookup and packet forwarding

- Error detection and correction

- Fragmentation, segmentation, and reassembly

- Frame and protocol demultiplexing

- Packet classification

- Queueing and packet discard

- Scheduling and timing

- Security: authentication and privacy

- Traffic measurement, policing, and shaping

#### **Address Lookup And Packet Forwarding**

- Forwarding requires address lookup

- Lookup is table driven

- Two types

- Exact match (typically layer 2)

- Longest-prefix match (typically layer 3)

- Cost depends on size of table and type of lookup

#### **Error Detection And Correction**

- Data sent with packet used as verification

- Checksum

- CRC

- Cost proportional to size of packet

- Often implemented with special-purpose hardware

#### **An Important Note About Cost**

The cost of an operation is proportional to the amount of data processed. An operation such as checksum computation that requires examination of all the data in a packet is among the most expensive.

### Fragmentation, Segmentation, And Reassembly

- IP fragments and reassembles datagrams

- ATM segments and reassembles AAL5 packets

- Same idea; details differ

- Cost is high because

- State must be kept and managed

- Unreassembled fragments occupy memory

#### Frame And Protocol Demultiplexing

- Traditional technique used in layered protocols

- Type appears in each header

- Assigned on output

- Used on input to select "next" protocol

- Cost of demultiplexing proportional to number of layers

#### **Packet Classification**

- Alternative to demultiplexing

- Crosses multiple layers

- Achieves lower cost

- More on classification later in the course

### **Queueing And Packet Discard**

- General paradigm is store-and-forward

- Incoming packet placed in queue

- Outgoing packet placed in queue

- When queue is full, choose packet to discard

- Affects throughput of higher-layer protocols

#### **Queueing Priorities**

- Multiple queues used to enforce priority among packets

- Incoming packet

- Assigned priority as function of contents

- Placed in appropriate priority queue

- Queueing discipline

- Examines priority queues

- Chooses which packet to send

#### **Examples Of Queueing Disciplines**

- Priority Queueing

- Assign unique priority number to each queue

- Choose packet from highest priority queue that is nonempty

- Known as strict priority queueing

- Can lead to starvation

# **Examples Of Queueing Disciplines** (continued)

- Weighted Round Robin (WRR)

- Assign unique priority number to each queue

- Process all queues round-robin

- Compute N, max number of packets to select from a queue proportional to priority

- Take up to N packets before moving to next queue

- Works well if all packets equal size

# **Examples Of Queueing Disciplines** (continued)

- Weighted Fair Queueing (WFQ)

- Make selection from queue proportional to priority

- Use packet size rather than number of packets

- Allocates priority to amount of data from a queue rather than number of packets

#### **Scheduling And Timing**

- Important mechanisms

- Used to coordinate parallel and concurrent tasks

- Processing on multiple packets

- Processing on multiple protocols

- Multiple processors

- Scheduler attempts to achieve fairness

#### **Security: Authentication And Privacy**

- Authentication mechanisms

- Ensure sender's identity

- Confidentiality mechanisms

- Ensure that intermediaries cannot interpret packet contents

- Note: in common networking terminology, *privacy* refers to confidentiality

- Example: Virtual Private Networks

### **Traffic Measurement And Policing**

- Used by network managers

- Can measure aggregate traffic or per-flow traffic

- Often related to Service Level Agreement (SLA)

- Cost is high if performed in real-time

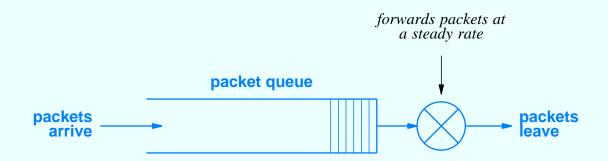

#### **Traffic Shaping**

- Make traffic conform to statistical bounds

- Typical use

- Smooth bursts

- Avoid packet trains

- Only possibilities

- Discard packets (seldom used)

- Delay packets

### **Example Traffic Shaping Mechanisms**

- Leaky bucket

- Easy to implement

- Popular

- Sends steady number of packets per second

- Rate depends on number of packets waiting

- Does not guarantee steady data rate

# **Example Traffic Shaping Mechanisms** (continued)

- Token bucket

- Sends steady number of bits per second

- Rate depends on number of bits waiting

- Achieves steady data rate

- More difficult to implement

#### **Illustration Of Traffic Shaper**

- Packets

- Arrive in bursts

- Leave at steady rate

#### **Timer Management**

- Fundamental piece of network system

- Needed for

- Scheduling

- Traffic shaping

- Other protocol processing (e.g., retransmission)

- Cost

- Depends on number of timer operations (e.g., set, cancel)

- Can be high

2003

#### **Summary**

- Primary packet processing functions are

- Address lookup and forwarding

- Error detection and correction

- Fragmentation and reassembly

- Demultiplexing and classification

- Queueing and discard

- Scheduling and timing

- Security functions

- Traffic measurement, policing, and shaping

#### VII

# **Protocol Software On A Conventional Processor**

## Possible Implementations Of Protocol Software

- In an application program

- Easy to program

- Runs as user-level process

- No direct access to network devices

- High cost to copy data from kernel address space

- Cannot run at wire speed

# Possible Implementations Of Protocol Software (continued)

- In an embedded system

- Special-purpose hardware device

- Dedicated to specific task

- Ideal for stand-alone system

- Software has full control

# Possible Implementations Of Protocol Software (continued)

- In an embedded system

- Special-purpose hardware device

- Dedicated to specific task

- Ideal for stand-alone system

- Software has full control

- You will experience this in lab!

# Possible Implementations Of Protocol Software (continued)

- In an operating system kernel

- More difficult to program than application

- Runs with kernel privilege

- Direct access to network devices

#### **Interface To The Network**

- Known as *Application Program Interface (API)*

- Can be

- Asynchronous

- Synchronous

- Synchronous interface can use

- Blocking

- Polling

#### **Asynchronous API**

- Also known as event-driven

- Programmer

- Writes set of functions

- Specifies which function to invoke for each event type

- Programmer has no control over function invocation

- Functions keep state in shared memory

- Difficult to program

- Example: function f() called when packet arrives

### **Synchronous API Using Blocking**

- Programmer

- Writes main flow-of-control

- Explicitly invokes functions as needed

- Built-in functions block until request satisfied

- Example: function *wait\_for\_packet()* blocks until packet arrives

- Easier to program

### **Synchronous API Using Polling**

- Nonblocking form of synchronous API

- Each function call returns immediately

- Performs operation if available

- Returns error code otherwise

- Example: function *try\_for\_packet()* either returns next packet or error code if no packet has arrived

- Closer to underlying hardware

#### **Typical Implementations And APIs**

- Application program

- Synchronous API using blocking (e.g., socket API)

- Another application thread runs while an application blocks

- Embedded systems

- Synchronous API using polling

- CPU dedicated to one task

- Operating systems

- Asynchronous API

- Built on interrupt mechanism

#### **Example Asynchronous API**

- Design goals

- For use with network processor

- Simplest possible interface

- Sufficient for basic packet processing tasks

- Includes

- I/O functions

- Timer manipulation functions

# Example Asynchronous API (continued)

- Initialization and termination functions

- on\_startup()

- on\_shutdown()

- Input function (called asynchronously)

- recv\_frame()

- Output functions

- new\_fbuf()

- send\_frame()

# Example Asynchronous API (continued)

- Timer functions (called asynchronously)

- delayed\_call()

- periodic\_call()

- cancel\_call()

- Invoked by outside application

- console\_command()

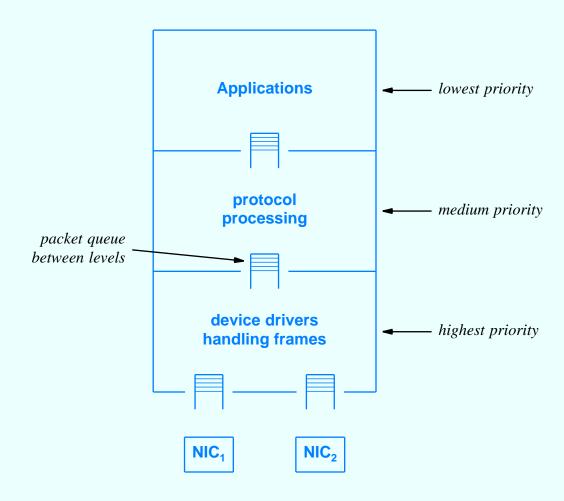

# **Processing Priorities**

- Determine which code CPU runs at any time

- General idea

- Hardware devices need highest priority

- Protocol software has medium priority

- Application programs have lowest priority

- Queues provide buffering across priorities

### **Illustration Of Priorities**

# Implementation Of Priorities In An Operating System

- Two possible approaches

- Interrupt mechanism

- Kernel threads

# **Interrupt Mechanism**

- Built into hardware

- Operates asynchronously

- Saves current processing state

- Changes processor status

- Branches to specified location

# **Two Types Of Interrupts**

- *Hardware interrupt*

- Caused by device (bus)

- Must be serviced quickly

- Software interrupt

- Caused by executing program

- Lower priority than hardware interrupt

- Higher priority than other OS code

# Software Interrupts And Protocol Code

- Protocol stack operates as software interrupt

- When packet arrives

- Hardware interrupts

- Device driver raises software interrupt

- When device driver finishes

- Hardware interrupt clears

- Protocol code is invoked

#### **Kernel Threads**

- Alternative to interrupts

- Familiar to programmer

- Finer-grain control than software interrupts

- Can be assigned arbitrary range of priorities

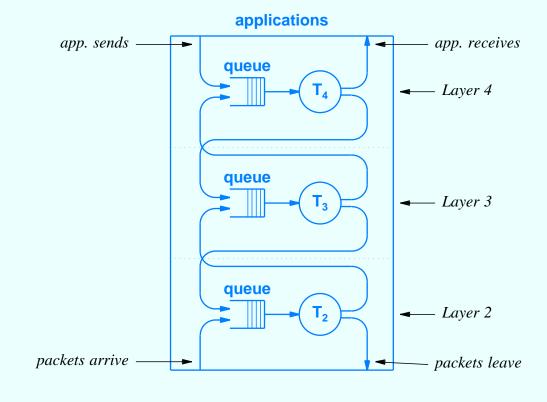

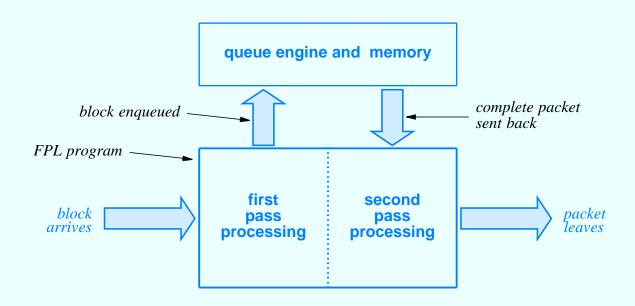

# **Conceptual Organization**

- Packet passes among multiple threads of control

- Queue of packets between each pair of threads

- Threads synchronize to access queues

# Possible Organization Of Kernel Threads For Layered Protocols

- One thread per layer

- One thread per protocol

- Multiple threads per protocol

- Multiple threads per protocol plus timer management thread(s)

- One thread per packet

# **One Thread Per Layer**

- Easy for programmer to understand

- Implementation matches concept

- Allows priority to be assigned to each layer

- Means packet is enqueued once per layer

# **Illustration Of One Thread Per Layer**

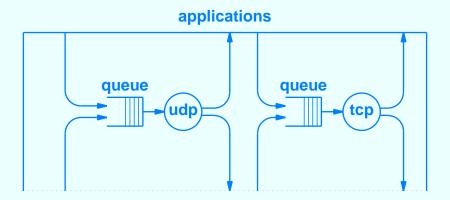

#### **One Thread Per Protocol**

- Like one thread per layer

- Implementation matches concept

- Means packet is enqueued once per layer

- Advantages over one thread per layer

- Easier for programmer to understand

- Finer-grain control

- Allows priority to be assigned to each protocol

#### **Illustration Of One Thread Per Protocol**

- TCP and UDP reside at same layer

- Separation allows priority

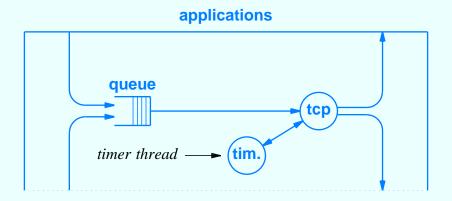

# **Multiple Threads Per Protocol**

- Further division of duties

- Simplifies programming

- More control than single thread

- Typical division

- Thread for incoming packets

- Thread for outgoing packets

- Thread for management/timing

# **Illustration Of Multiple Threads Used With TCP**

• Separate timer makes programming easier

#### **Timers And Protocols**

- Many protocols implement timeouts

- TCP

- \* Retransmission timeout

- \* 2MSL timeout

- ARP

- \* Cache entry timeout

- IP

- \* Reassembly timeout

# Multiple Threads Per Protocol Plus Timer Management Thread(s)

- Observations

- Many protocols each need timer functionality

- Each timer thread incurs overhead

- Solution: consolidate timers for multiple protocols

#### Is One Timer Thread Sufficient?

- In theory

- Yes

- In practice

- Large range of timeouts (microseconds to tens of seconds)

- May want to give priority to some timeouts

- Solution: two or more timer threads

# **Multiple Timer Threads**

- Two threads usually suffice

- Large-granularity timer

- Values specified in seconds

- Operates at lower priority

- Small-granularity timer

- Values specified in microseconds

- Operates at higher priority

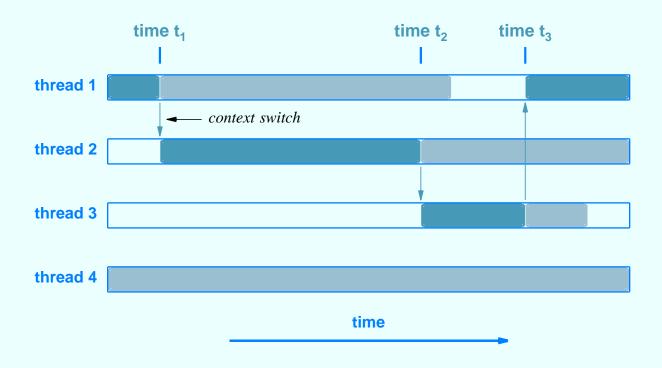

# **Thread Synchronization**

- Thread for layer *i*

- Needs to pass a packet to layer i + 1

- Enqueues the packet

- Thread for layer i + 1

- Retrieves packet from the queue

# **Thread Synchronization**

- Thread for layer *i*

- Needs to pass a packet to layer i + 1

- Enqueues the packet

- Thread for layer i + 1

- Retrieves packet from the queue

- Context switch required!

#### **Context Switch**

- OS function

- CPU passes from current thread to a waiting thread

- High cost

- Must be minimized

#### **One Thread Per Packet**

- Preallocate set of threads

- Thread operation

- Waits for packet to arrive

- Moves through protocol stack

- Returns to wait for next packet

- Minimizes context switches

# **Summary**

- Packet processing software usually runs in OS

- API can be synchronous or asynchronous

- Priorities achieved with

- Software interrupts

- Threads

- Variety of thread architectures possible

#### VIII

# Hardware Architectures For Protocol Processing And Aggregate Rates

# A Brief History Of Computer Hardware

- 1940s

- Beginnings

- 1950s

- Consolidation on von Neumann architecture

- I/O controlled by CPU

- 1960s

- I/O becomes important

- Evolution of third generation architecture with interrupts

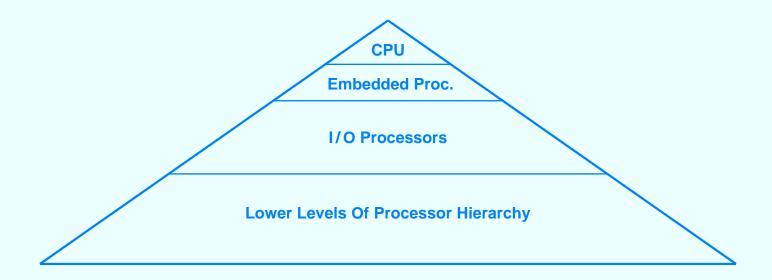

# I/O Processing

- Evolved from after-thought to central influence

- Low-end systems (e.g., microcontrollers)

- Dumb I/O interfaces

- CPU does all the work (polls devices)

- Single, shared memory

- Low cost, but low speed

# I/O Processing (continued)

- Mid-range systems (e.g., minicomputers)

- Single, shared memory

- I/O interfaces contain logic for transfer and status operations

- CPU

- \* Starts device then resumes processing

- Device

- \* Transfers data to / from memory

- \* Interrupts when operation complete

# I/O Processing (continued)

- High-end systems (e.g., mainframes)

- Separate, programmable I/O processor

- OS downloads code to be run

- Device has private on-board buffer memory

- Examples: IBM channel, CDC peripheral processor

# **Networking Systems Evolution**

- Twenty year history

- Same trend as computer architecture

- Began with central CPU

- Shift to emphasis on I/O

- Three main generations

# **First Generation Network Systems**

- Traditional software-based router

- Used conventional (minicomputer) hardware

- Single general-purpose processor

- Single shared memory

- I/O over a bus

- Network interface cards use same design as other I/O devices

# Protocol Processing In First Generation Network Systems

- General-purpose processor handles most tasks

- Sufficient for low-speed systems

- Note: we will examine other generations later in the course

#### **How Fast Does A CPU Need To Be?**

- Depends on

- Rate at which data arrives

- Amount of processing to be performed

# Two Measures Of Speed

- Data rate (bits per second)

- Per interface rate

- Aggregate rate

- Packet rate (packets per second)

- Per interface rate

- Aggregate rate

#### **How Fast Is A Fast Connection?**

Definition of fast data rate keeps changing

– 1960: 10 Kbps

- 1970: 1 Mbps

- 1980: 10 Mbps

- 1990: 100 Mbps

- 2000: 1000 Mbps (1 Gbps)

- 2003: 2400 Mbps

#### **How Fast Is A Fast Connection?**

Definition of fast data rate keeps changing

– 1960: 10 Kbps

- 1970: 1 Mbps

- 1980: 10 Mbps

- 1990: 100 Mbps

- 2000: 1000 Mbps (1 Gbps)

- 2003: 2400 Mbps

– Soon: 10 Gbps???

# Aggregate Rate Vs. Per-Interface Rate

- Interface rate

- Rate at which data enters / leaves

- Aggregate

- Sum of interface rates

- Measure of total data rate system can handle

- Note: aggregate rate crucial if CPU handles traffic from all interfaces

# A Note About System Scale

The aggregate data rate is defined to be the sum of the rates at which traffic enters or leaves a system. The maximum aggregate data rate of a system is important because it limits the type and number of network connections the system can handle.

## Packet Rate Vs. Data Rate

- Sources of CPU overhead

- Per-bit processing

- Per-packet processing

- Interface hardware handles much of per-bit processing

# A Note About System Scale

For protocol processing tasks that have a fixed cost per packet, the number of packets processed is more important than the aggregate data rate.

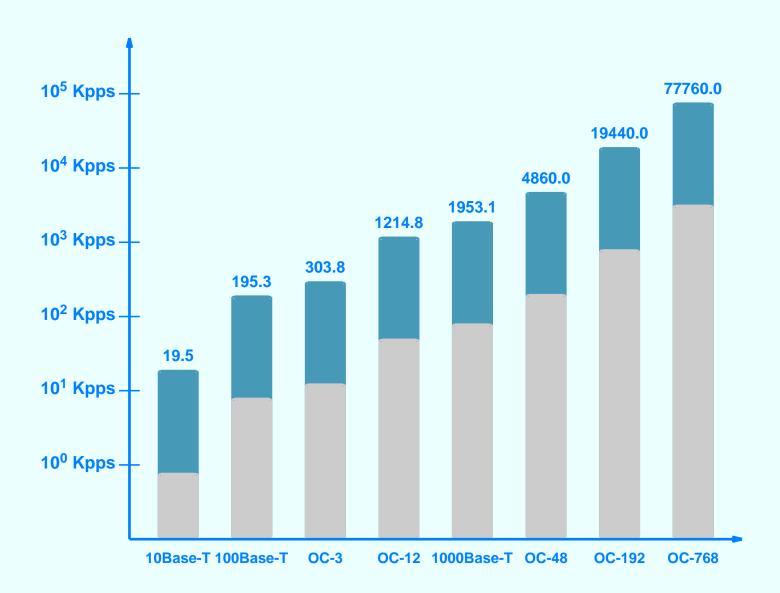

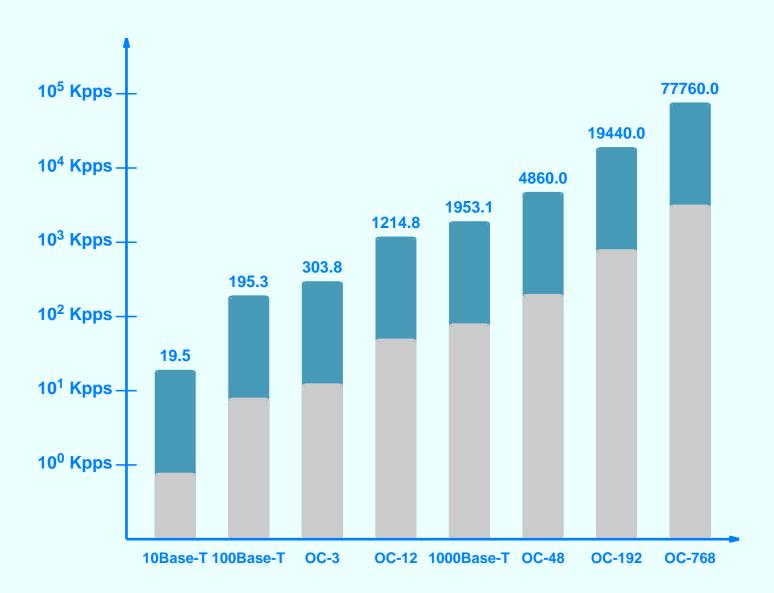

# **Example Packet Rates**

| Technology | Network<br>Data Rate<br>In Gbps | Packet Rate<br>For Small Packets<br>In Kpps | Packet Rate<br>For Large Packets<br>In Kpps |

|------------|---------------------------------|---------------------------------------------|---------------------------------------------|

| 10Base-T   | 0.010                           | 19.5                                        | 0.8                                         |

| 100Base-T  | 0.100                           | 195.3                                       | 8.2                                         |

| OC-3       | 0.156                           | 303.8                                       | 12.8                                        |

| OC-12      | 0.622                           | 1,214.8                                     | 51.2                                        |

| 1000Base-T | 1.000                           | 1,953.1                                     | 82.3                                        |

| OC-48      | 2.488                           | 4,860.0                                     | 204.9                                       |

| OC-192     | 9.953                           | 19,440.0                                    | 819.6                                       |

| OC-768     | 39.813                          | 77,760.0                                    | 3,278.4                                     |

• Key concept: maximum packet rate occurs with minimum-size packets

# **Bar Chart Of Example Packet Rates**

# **Bar Chart Of Example Packet Rates**

Gray areas show rates for large packets

## **Time Per Packet**

| Technology | Time per packet for small packets (in μs) | Time per packet for large packets (in μs) |

|------------|-------------------------------------------|-------------------------------------------|

| 10Base-T   | 51.20                                     | 1,214.40                                  |

| 100Base-T  | 5.12                                      | 121.44                                    |

| OC-3       | 3.29                                      | 78.09                                     |

| OC-12      | 0.82                                      | 19.52                                     |

| 1000Base-T | 0.51                                      | 12.14                                     |

| OC-48      | 0.21                                      | 4.88                                      |

| OC-192     | 0.05                                      | 1.22                                      |

| OC-768     | 0.01                                      | 0.31                                      |

• Note: these numbers are for a single connection!

#### **Conclusion**

Software running on a general-purpose processor is an insufficient architecture to handle high-speed networks because the aggregate packet rate exceeds the capabilities of a CPU.

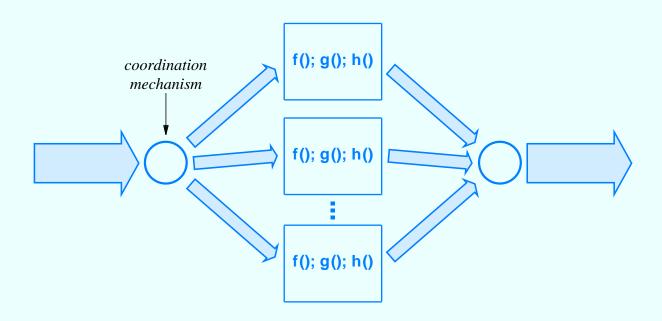

# Possible Ways To Solve The CPU Bottleneck

- Fine-grain parallelism

- Symmetric coarse-grain parallelism

- Asymmetric coarse-grain parallelism

- Special-purpose coprocessors

- NICs with onboard processing

- Smart NICs with onboard stacks

- Cell switching

- Data pipelines

### **Fine-Grain Parallelism**

- Multiple processors

- Instruction-level parallelism

- Example:

- Parallel checksum: add values of eight consecutive memory locations at the same time

- Assessment: insignificant advantages for packet processing

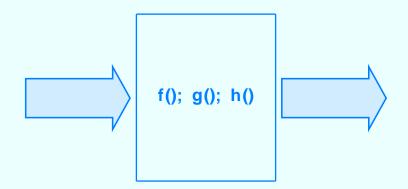

# Symmetric Coarse-Grain Parallelism

- Symmetric multiprocessor hardware

- Multiple, identical processors

- Typical design: each CPU operates on one packet

- Requires coordination

- Assessment: coordination and data access means *N* processors cannot handle *N* times more packets than one processor

# Asymmetric Coarse-Grain Parallelism

- Multiple processors

- Each processor

- Optimized for specific task

- Includes generic instructions for control

- Assessment

- Same problems of coordination and data access as symmetric case

- Designer much choose how many copies of each processor type

# **Special-Purpose Coprocessors**

- Special-purpose hardware

- Added to conventional processor to speed computation

- Invoked like software subroutine

- Typical implementation: ASIC chip

- Choose operations that yield greatest improvement in speed

# **General Principle**

To optimize computation, move operations that account for the most CPU time from software into hardware.

# **General Principle**

To optimize computation, move operations that account for the most CPU time from software into hardware.

• Idea known as *Amdahl's law* (performance improvement from faster hardware technology is limited to the fraction of time the faster technology can be used)

# **NICs And Onboard Processing**

- Basic optimizations

- Onboard address recognition and filtering

- Onboard buffering

- DMA

- Buffer and operation chaining

- Further optimization possible

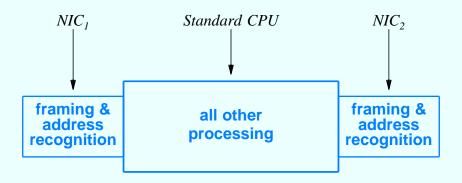

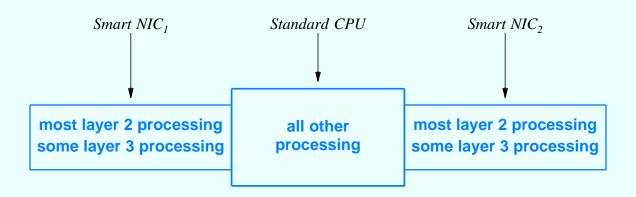

## **Smart NICs With Onboard Stacks**

- Add hardware to NIC

- Off-the-shelf chips for layer 2

- ASICs for layer 3

- Allows each NIC to operate independently

- Effectively a multiprocessor

- Total processing power increased dramatically

# **Illustration Of Smart NICs With Onboard Processing**

- NIC handles layers 2 and 3

- CPU only handles exceptions

# **Cell Switching**

- Alternative to new hardware

- Changes

- Basic paradigm

- All details (e.g., protocols)

- Connection-oriented

# **Cell Switching Details**

- Fixed-size packets

- Allows fixed-size buffers

- Guaranteed time to transmit/receive

- Relative (connection-oriented) addressing

- Smaller address size

- Label on packet changes at each switch

- Requires connection setup

- Example: ATM

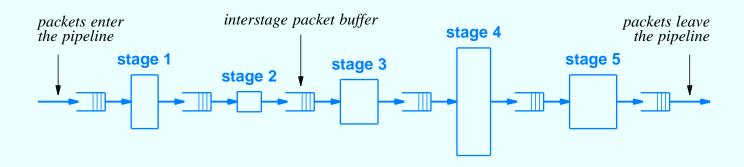

# **Data Pipeline**

- Move each packet through series of processors

- Each processor handles some tasks

- Assessment

- Well-suited to many protocol processing tasks

- Individual processor can be fast

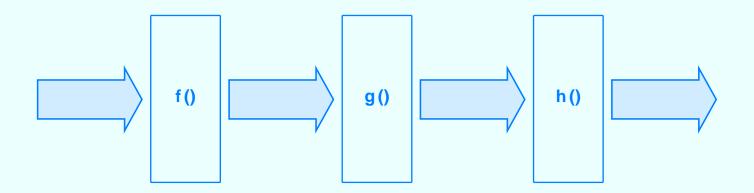

# **Illustration Of Data Pipeline**

- Pipeline can contain heterogeneous processors

- Packets pass through each stage

# **Summary**

- Packet rate can be more important than data rate

- Highest packet rate achieved with smallest packets

- Rates measured per interface or aggregate

- Special hardware needed for highest-speed network systems

- Smart NIC can include part of protocol stack

- Parallel and pipelined hardware also possible

## IX

# Classification And Forwarding

## Recall

- Packet demultiplexing

- Used with layered protocols

- Packet proceeds through one layer at a time

- On input, software in each layer chooses module at next higher layer

- On output, type field in each header specifies encapsulation

# The Disadvantage Of Demultiplexing

Although it provides freedom to define and use arbitrary protocols without introducing transmission overhead, demultiplexing is inefficient because it imposes sequential processing among layers.

### **Packet Classification**

- Alternative to demultiplexing

- Designed for higher speed

- Considers all layers at the same time

- Linear in number of fields

- Two possible implementations

- Software

- Hardware

# **Example Classification**

- Classify Ethernet frames carrying traffic to Web server

- Specify exact header contents in *rule set*

- Example

- Ethernet type field specifies IP

- IP type field specifies TCP

- TCP destination port specifies Web server

# **Example Classification** (continued)

- Field sizes and values

- 2-octet Ethernet type is 0800<sub>16</sub>

- 2-octet IP type is 6

- 2-octet TCP destination port is 80

# **Illustration Of Encapsulated Headers**

Highlighted fields are used for classification of Web server traffic

# Software Implementation Of Classification

- Compare values in header fields

- Conceptually a *logical and* of all field comparisons

- Example

```

if ((frame type == 0x0800) && (IP type == 6) && (TCP port == 80))

declare the packet matches the classification;

else

declare the packet does not match the classification;

```

# **Optimizing Software Classification**

- Comparisons performed sequentially

- Can reorder comparisons to minimize effort

# **Example Of Optimizing Software Classification**

- Assume

- 95.0% of all frames have frame type  $0800_{16}$

- 87.4% of all frames have IP type 6

- 74.3% of all frames have TCP port 80

- Also assume values 6 and 80 do not occur in corresponding positions in non-IP packet headers

- Reordering tests can optimize processing time

# **Example Of Optimizing Software Classification** (continued)

```

if ((TCP port == 80) && (IP type == 6) && (frame type == 0x0800))

declare the packet matches the classification;

else

declare the packet does not match the classification;

```

• At each step, test the field that will eliminate the most packets

#### **Note About Optimization**

Although the maximum number of comparisons in a software classifier is fixed, the average number of comparisons is determined by the order of the tests; minimum comparisons result if, at each step, the classifier tests the field that eliminates the most packets.

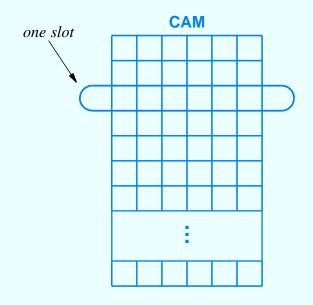

## **Hardware Implementation Of Classification**

- Can build special-purpose hardware

- Steps

- Extract needed fields

- Concatenate bits

- Place result in register

- Perform comparison

- Hardware can operate in parallel

#### **Illustration Of Hardware Classifier**

• Constant for Web classifier is 08.00.06.01.50<sub>16</sub>

# **Special Cases Of Classification**

- Multiple categories

- Variable-size headers

- Dynamic classification

#### In Practice

- Classification usually involves multiple categories

- Packets grouped together into *flows*

- May have a default category

- Each category specified with rule set

## **Example Multi-Category Classification**

- Flow 1: traffic destined for Web server

- Flow 2: traffic consisting of ICMP echo request packets

- Flow 3: all other traffic (default)

#### **Rule Sets**

- Web server traffic

- 2-octet Ethernet type is 0800<sub>16</sub>

- 2-octet IP type is 6

- 2-octet TCP destination port is 80

- ICMP echo traffic

- 2-octet Ethernet type is 0800<sub>16</sub>

- 2-octet IP type is 1

- 1-octet ICMP type is 8

#### **Software Implementation Of Multiple Rules**

```

if (frame type != 0x0800) {

send frame to flow 3;

} else if (IP type == 6 && TCP destination port == 80) {

send packet to flow 1;

} else if (IP type == 1 && ICMP type == 8) {

send packet to flow 2;

} else {

send frame to flow 3;

}

```

Further optimization possible

#### Variable-Size Packet Headers

- Fields not at fixed offsets

- Easily handled with software

- Finite cases can be specified in rules

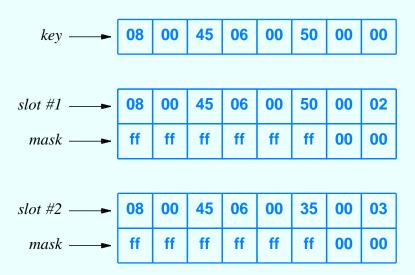

## **Example Variable-Size Header: IP Options**

#### • Rule Set 1

- 2-octet frame type field contains 0800<sub>16</sub>

- 1-octet field at the start of the datagram contains 45<sub>16</sub>

- 1-octet type field in the IP datagram contains 6

- 2-octet field 22 octets from start of the datagram contains 80

#### • Rule Set 2

- 2-octet frame type field contains 0800<sub>16</sub>

- 1-octet field at the start of the datagram contains 46<sub>16</sub>

- 1-octet type field in the IP datagram contains 6

- 2-octet field 26 octets from the start of datagram contains 80

# **Effect Of Protocol Design On Classification**

- Fixed headers fastest to classify

- Each variable-size header adds one computation step

- In worst case, classification no faster than demultiplexing

- Extreme example: IPv6

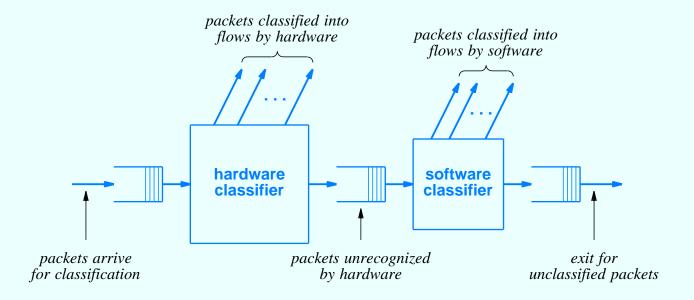

#### **Hybrid Classification**

- Combines hardware and software mechanisms

- Hardware used for standard cases

- Software used for exceptions

- Note: software classifier can operate at slower rate

## **Two Basic Types Of Classification**

#### • Static

- Flows specified in rule sets

- Header fields and values known a priori

#### Dynamic

- Flows created by observing packet stream

- Values taken from headers

- Allows fine-grain flows

- Requires state information

## **Example Static Classification**

- Allocate one flow per service type

- One header field used to identify flow

- IP TYPE OF SERVICE (TOS)

- Use DIFFSERV interpretation

- Note: Ethernet type field also checked

# **Example Dynamic Classification**

- Allocate flow per TCP connection

- Header fields used to identify flow

- IP source address

- IP destination address

- TCP source port number

- TCP destination port number

- Note: Ethernet type and IP type fields also checked

## Implementation Of Dynamic Classification

- Usually performed in software

- State kept in memory

- State information created/updated at wire speed

## **Two Conceptual Bindings**

classification: packet  $\rightarrow$  flow

forwarding:  $flow \rightarrow packet disposition$

- Classification binding is usually 1-to-1

- Forwarding binding can be 1-to-1 or many-to-1

#### **Flow Identification**

- Connection-oriented network

- Per-flow SVC can be created on demand

- Flow ID equals connection ID

- Connectionless network

- Flow ID used internally

- Each flow ID mapped to (next hop, interface)

#### Relationship Of Classification And Forwarding In A Connection-Oriented Network

In a connection-oriented network, flow identifiers assigned by classification can be chosen to match connection identifiers used by the underlying network. Doing so makes forwarding more efficient by eliminating one binding.

# Forwarding In A Connectionless Network

- Route for flow determined when flow created

- Indexing used in place of route lookup

- Flow identifier corresponds to index of entry in forwarding cache

- Forwarding cache must be changed when route changes

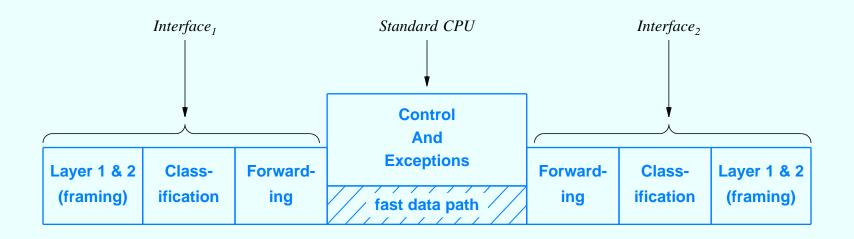

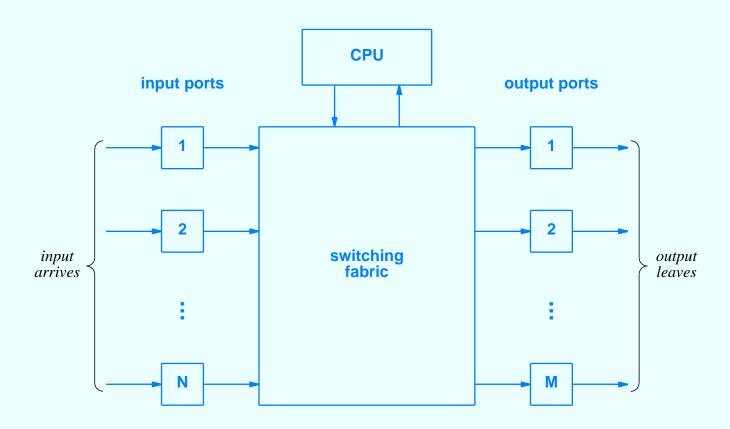

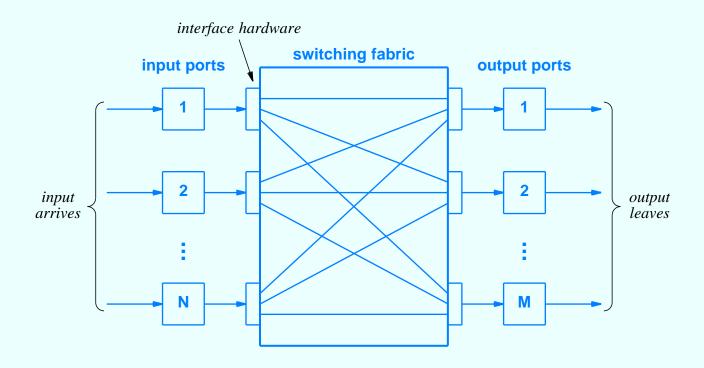

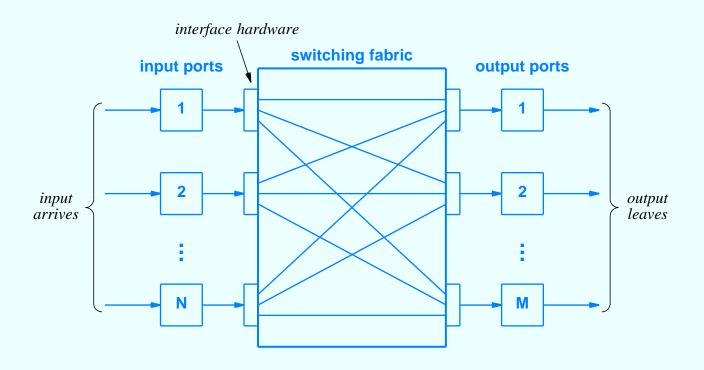

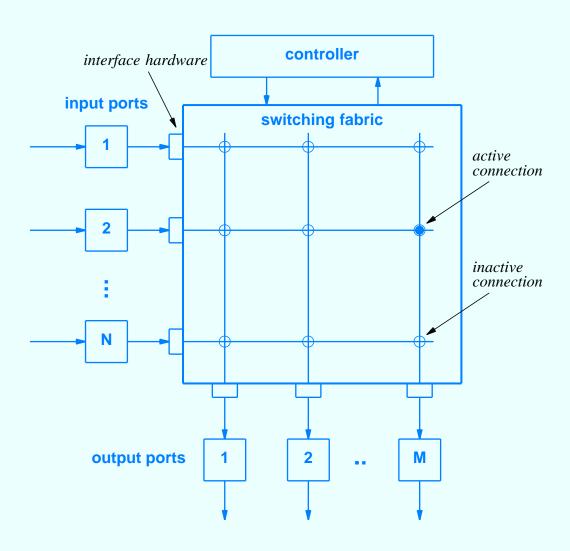

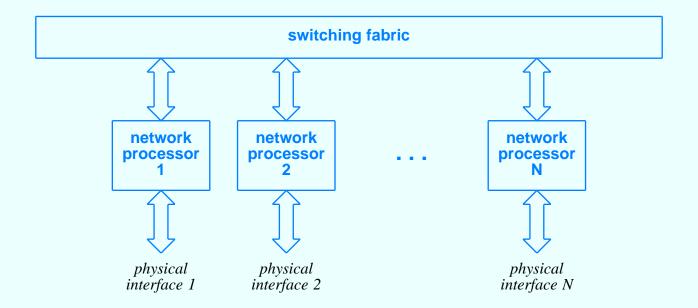

## **Second Generation Network Systems**

- Designed for greater scale

- Use classification instead of demultiplexing

- Decentralized architecture

- Additional computational power on each NIC

- NIC implements classification and forwarding

- High-speed internal interconnection mechanism

- Interconnects NICs

- Provides fast data path

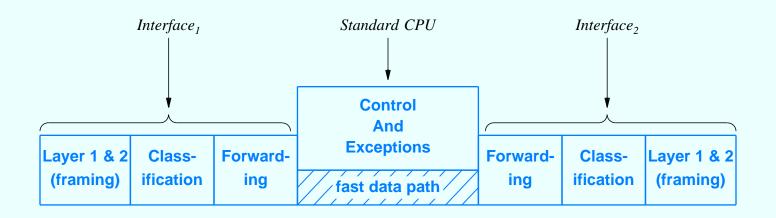

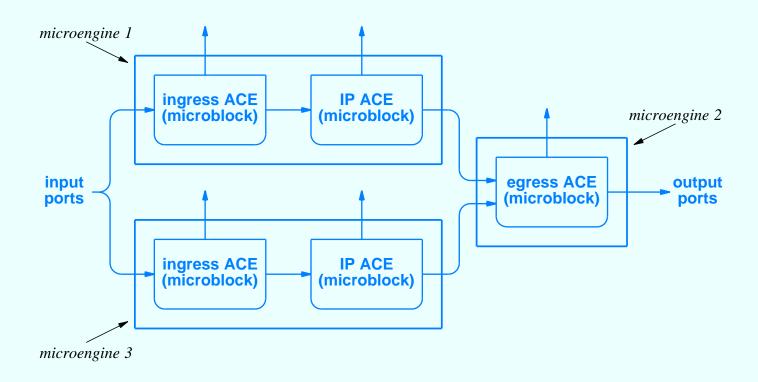

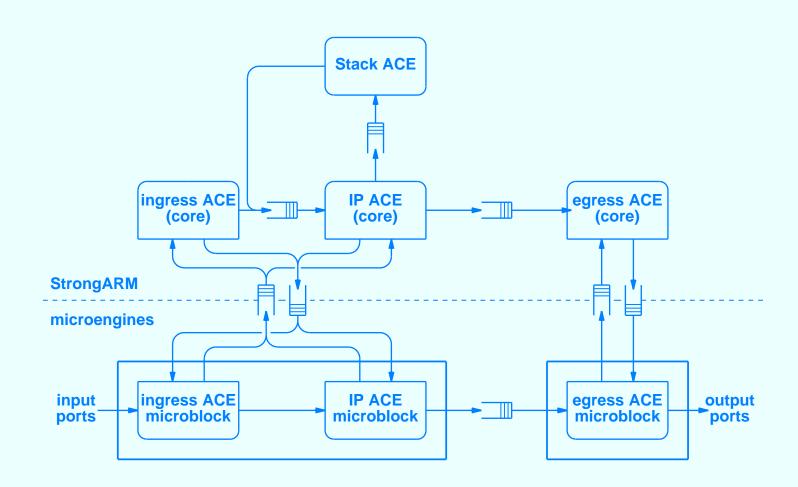

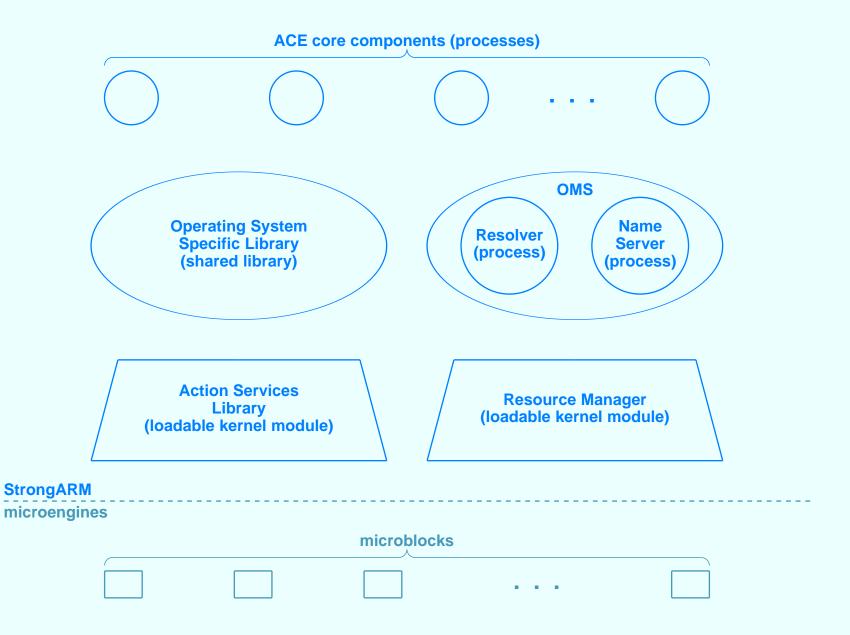

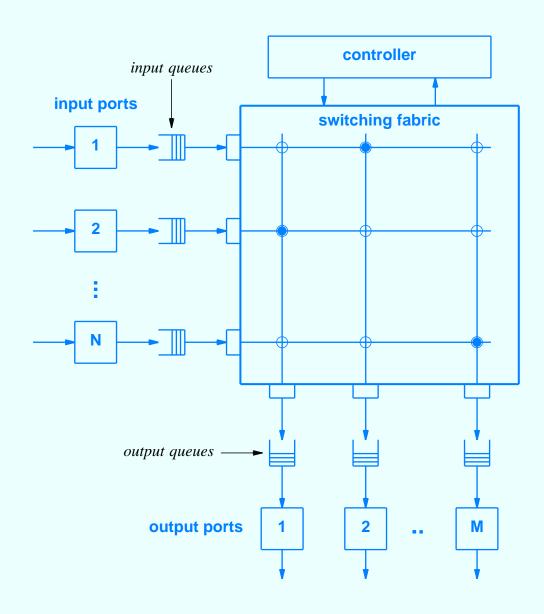

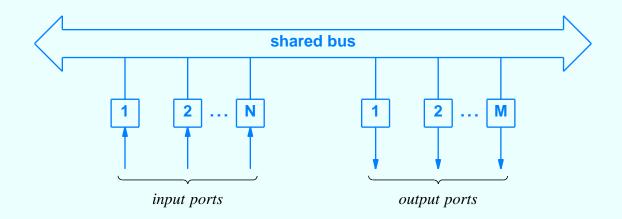

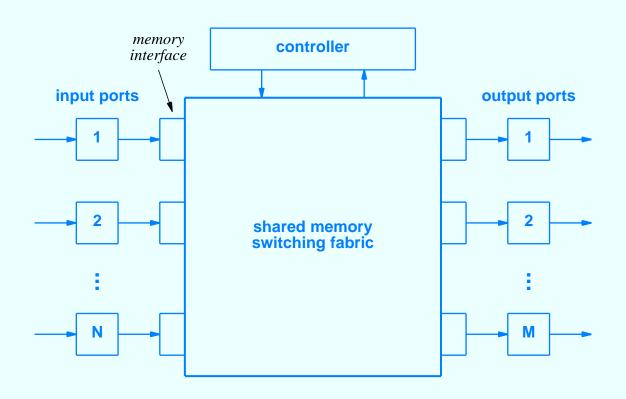

# Illustration Of Second Generation Network Systems Architecture

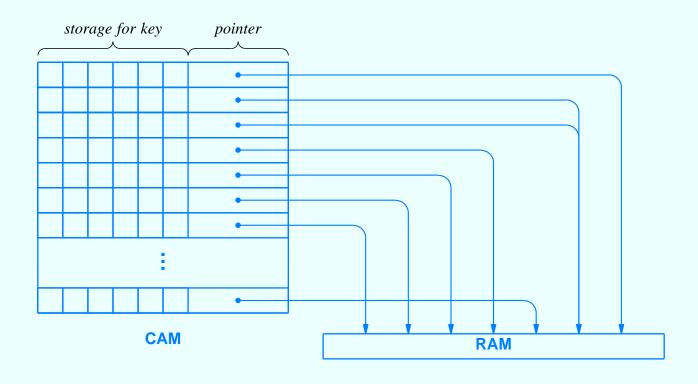

## **Classification And Forwarding Chips**

- Sold by vendors

- Implement hardware classification and forwarding

- Typical configuration: rule sets given in ROM

## **Summary**

- Classification faster than demultiplexing

- Can be implemented in hardware or software

- Dynamic classification

- Uses packet contents to assign flows

- Requires state information

#### XI

**Network Processors: Motivation And Purpose**

#### **Second Generation Network Systems**

- Concurrent with ATM development (early 1990s)

- Purpose: scale to speeds faster than single CPU capacity

- Features

- Use classification instead of demultiplexing

- Decentralized architecture to offload CPU

- Design optimized for fast data path

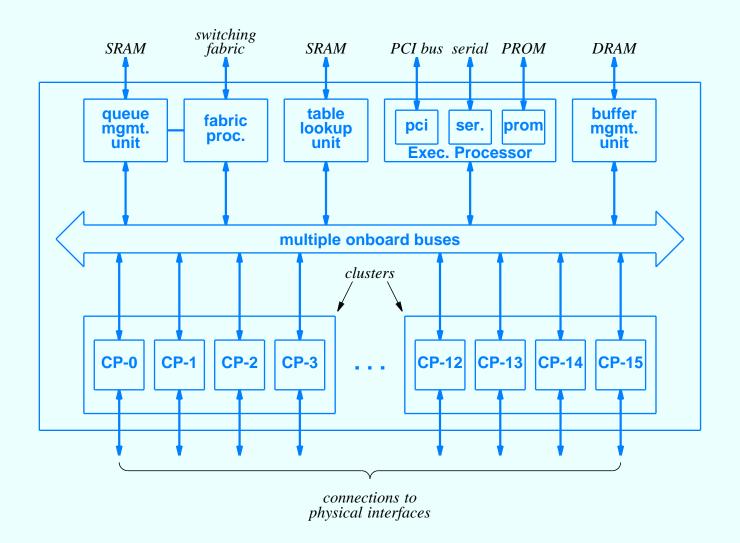

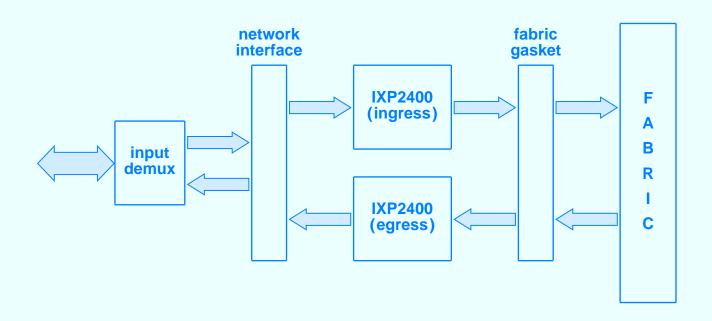

# **Second Generation Network Systems** (details)

- Multiple network interfaces

- Powerful NIC

- Private buffer memory

- High-speed hardware interconnects NICs

- General-purpose processor only handles exceptions

- Sufficient for medium speed interfaces (100 Mbps)

# Reminder: Protocol Processing In Second Generation Network Systems

- NIC handles most of layers 1 3

- Fast-path forwarding avoids CPU completely

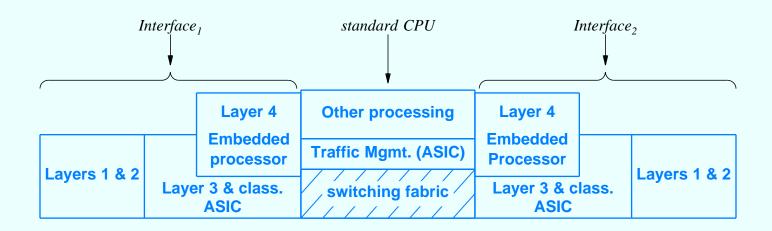

## **Third Generation Network Systems**

- Late 1990s

- Functionality partitioned further

- Additional hardware on each NIC

- Almost all packet processing off-loaded from CPU

## **Third Generation Design**

- NIC contains

- ASIC hardware

- Embedded processor plus code in ROM

- NIC handles

- Classification

- Forwarding

- Traffic policing

- Monitoring and statistics

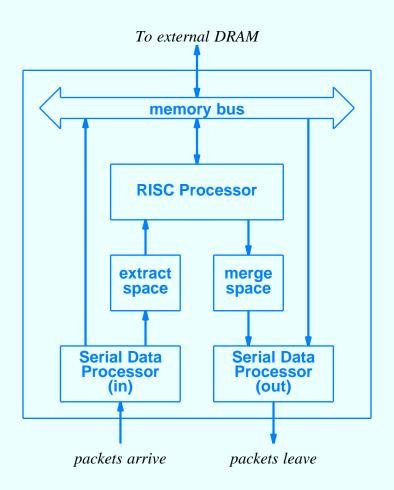

#### **Embedded Processor**

- Two possibilities

- Complex Instruction Set Computer (CISC)

- Reduced Instruction Set Computer (RISC)

- RISC used often because

- Higher clock rates

- Smaller

- Lower power consumption

# Purpose Of Embedded Processor In Third Generation Systems

Third generation systems use an embedded processor to handle layer 4 functionality and exception packets that cannot be forwarded across the fast path. An embedded processor architecture is chosen because ease of implementation and amenability to change are more important than speed.

#### **Protocol Processing In Third Generation Systems**

- Special-purpose ASICs handle lower layer functions

- Embedded (RISC) processor handles layer 4

- CPU only handles low-demand processing

# **Are Third Generation Systems Sufficient?**

# **Are Third Generation Systems Sufficient?**

Almost

# **Are Third Generation Systems Sufficient?**

• Almost ... but not quite.

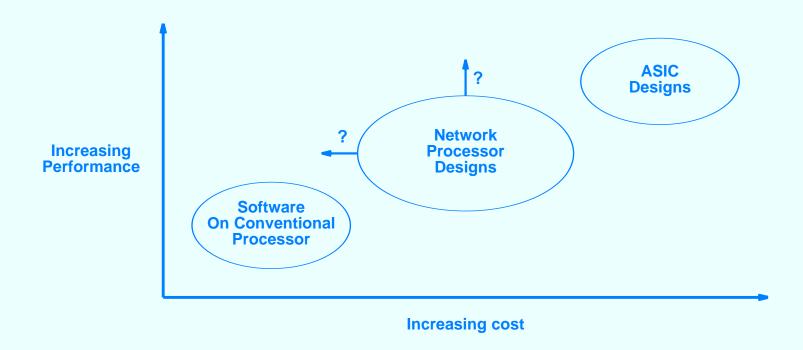

#### **Problems With Third Generation Systems**

- High cost

- Long time to market

- Difficult to simulate/test

- Expensive and time-consuming to change

- Even trivial changes require silicon respin

- 18-20 month development cycle

- Little reuse across products

- Limited reuse across versions

# **Problems With Third Generation Systems** (continued)

- No consensus on overall framework

- No standards for special-purpose support chips

- Requires in-house expertise (ASIC designers)

#### **A Fourth Generation**

- Goal: combine best features of first generation and third generation systems

- Flexibility of programmable processor

- High speed of ASICs

- Technology called *network processors*

#### **Definition Of A Network Processor**

A network processor is a special-purpose, programmable hardware device that combines the low cost and flexibility of a RISC processor with the speed and scalability of custom silicon (i.e., ASIC chips). Network processors are building blocks used to construct network systems.

### **Network Processors: Potential Advantages**

- Relatively low cost

- Straightforward hardware interface

- Facilities to access

- Memory

- Network interface devices

- Programmable

- Ability to scale to higher

- Data rates

- Packet rates

### **Network Processors: Potential Advantages**

- Relatively low cost

- Straightforward hardware interface

- Facilities to access

- Memory

- Network interface devices

- Programmable

- Ability to scale to higher

- Data rates

- Packet rates

### The Promise Of Programmability

- For producers

- Lower initial development costs

- Reuse software in later releases and related systems

- Faster time-to-market

- Same high speed as ASICs

- For consumers

- Much lower product cost

- Inexpensive (firmware) upgrades

#### **Choice Of Instruction Set**

- Programmability alone insufficient

- Also need higher speed

- Should network processors have

- Instructions for specific protocols?

- Instructions for specific protocol processing tasks?

- Choices difficult

#### **Instruction Set**

- Need to choose one instruction set

- No single instruction set best for all uses

- Other factors

- Power consumption

- Heat dissipation

- Cost

- More discussion later in the course

### **Scalability**

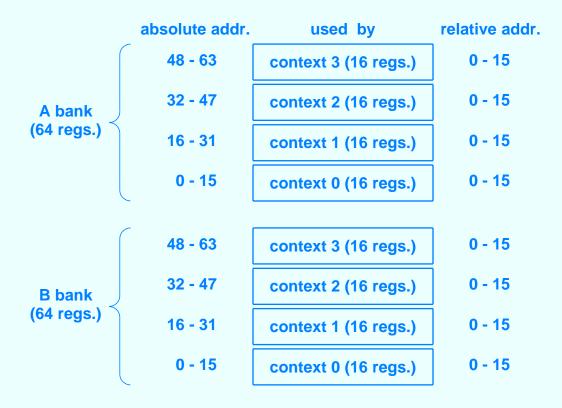

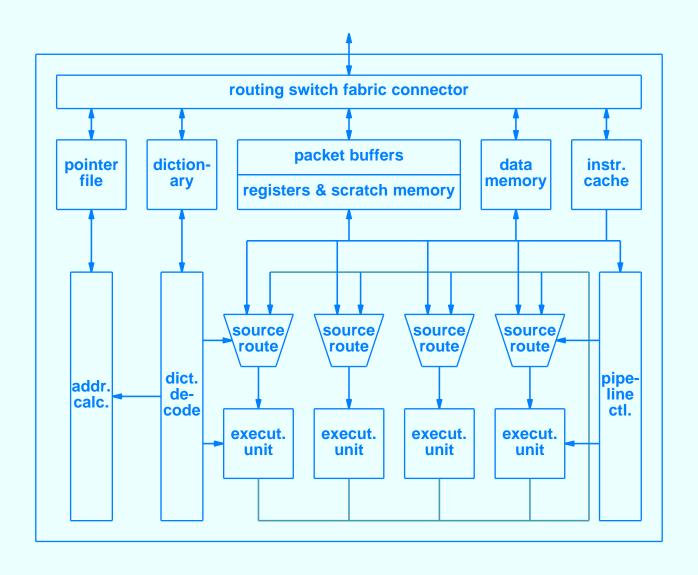

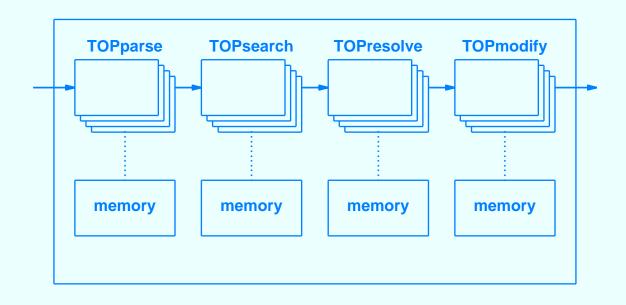

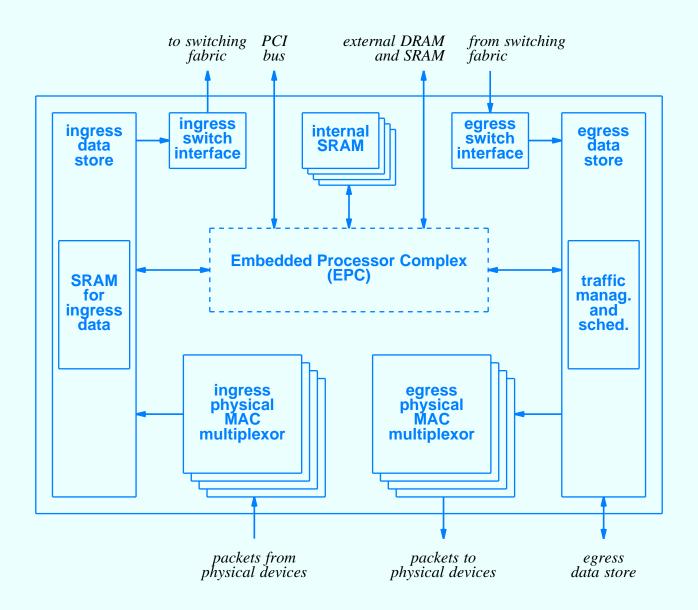

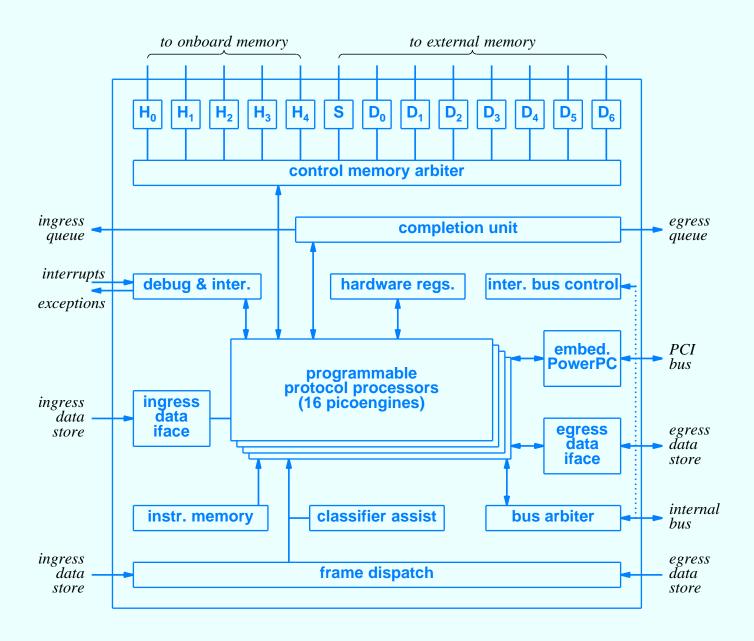

- Two primary techniques

- Parallelism

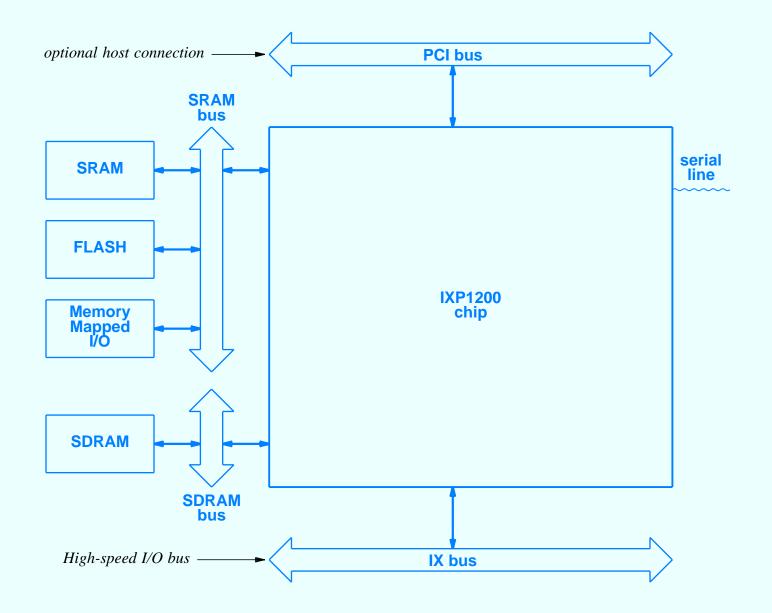

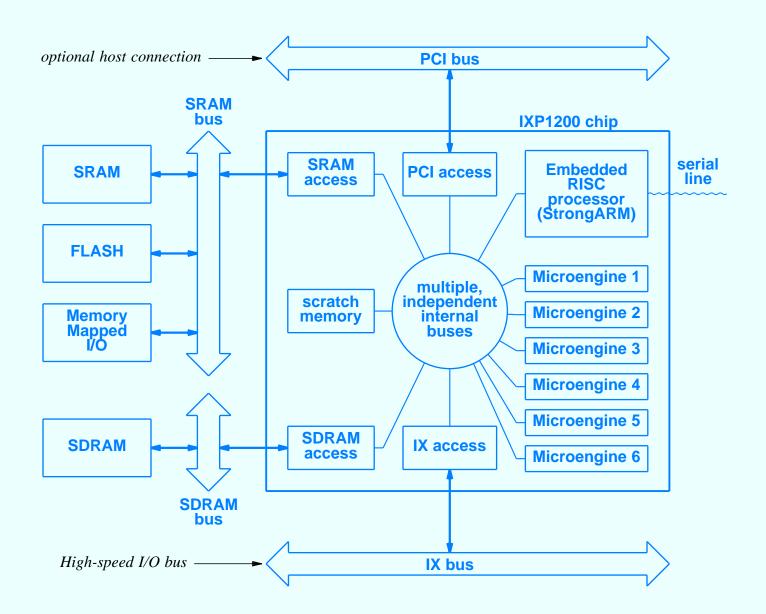

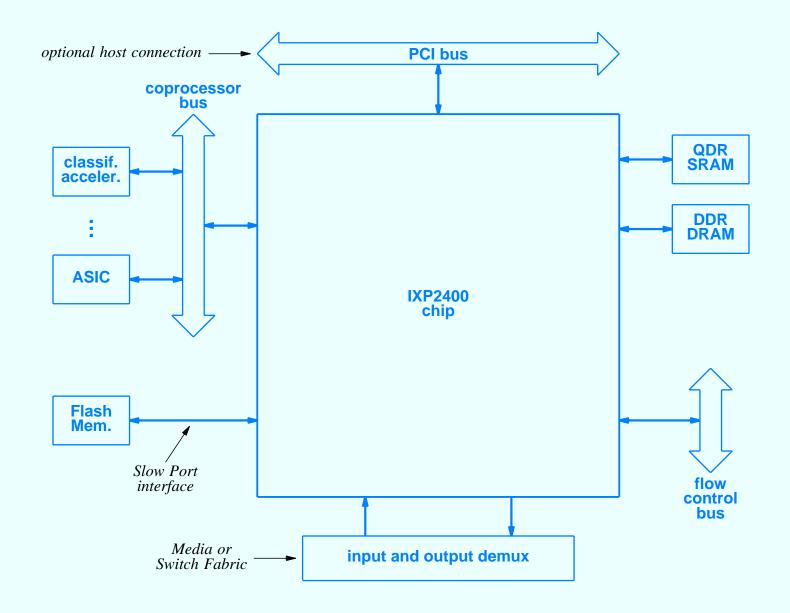

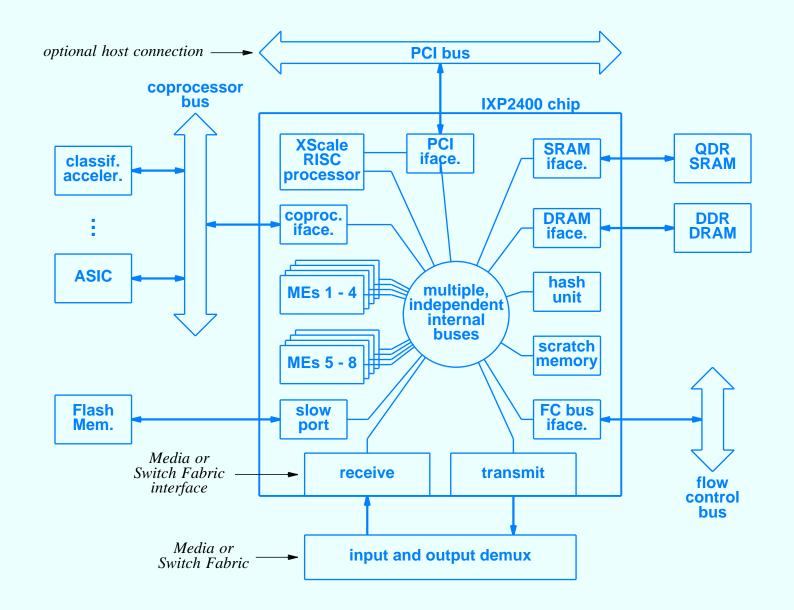

- Data pipelining